- Home /

- Publicaciones de patentes /

- CIRCUITO INTEGRADO FOTÓNICO HÍBRIDO Y MÉTODO DE FABRICACIÓN

Patente nacional por "CIRCUITO INTEGRADO FOTÓNICO HÍBRIDO Y MÉTODO DE FABRICACIÓN"

Este registro ha sido solicitado por

Persona física

a través del representanteGUILLERMO MENÉNDEZ GARCÍA

Contacto

- Estado: Vigente

- País:

- España

- Fecha solicitud:

- 16/02/2024

- Número solicitud:

-

P202430118

- Número publicación:

-

ES2963848

- Fecha de concesión:

-

- Inventores:

-

Persona física

- Datos del titular:

-

Persona física

- Datos del representante:

-

Guillermo Menéndez García

- Clasificación Internacional de Patentes:

- H01L 21/02,H01L 23/34,H01L 31/024

- Clasificación Internacional de Patentes de la publicación:

- H01L 21/02,H01L 23/34,H01L 31/024

- Fecha de vencimiento:

Quiero registrar una patente

Reivindicaciones:

+ ES-2963848_A11. Un circuito integrado fotónico híbrido (1) que comprende: a) una capa funcional fotónica de tecnología de silicio que comprende: - una superficie de silicio (2) , donde la superficie de silicio (2) comprende al menos un pilar de silicio (3) , donde el al menos un pilar de silicio (3) tiene dos bases, una base inferior y una base superior, donde la base inferior está dispuesta sobre la superficie de silicio (2) , y donde la superficie de silicio (2) y el al menos un pilar de silicio (3) forman, sin interrupción, una única pieza; - una capa de óxido de silicio (4) , donde la capa de óxido de silicio (4) comprende dos caras, una primera cara y una segunda cara, donde la primera cara está dispuesta sobre la superficie de silicio (2) , y donde la capa de óxido de silicio (4) está atravesada por el al menos un pilar de silicio (3) entre la primera cara y la segunda cara; - opcionalmente, una guía de onda (5) , donde la guía de onda (5) está comprendida en la capa de óxido de silicio (4) , y donde la guía de onda (5) no está en contacto directo ni con la superficie de silicio (2) ni con el al menos un pilar de silicio (3) ; y b) una capa de un semiconductor III-V (6) o un chip que se pueda hibridar con una tecnología de dieléctricos de silicio, donde la capa de semiconductor III-V (6) o el chip que se pueda hibridar con una tecnología de dieléctricos de silicio está en contacto con la base superior del al menos un pilar de silicio (3) , con la segunda cara de la capa de óxido de silicio (4) , y opcionalmente con la guía de onda (5) , y donde la capa de semiconductor III-V (6) o el chip que se pueda hibridar con una tecnología de dieléctricos de silicio no está atravesada por el al menos un pilar de silicio (3) , donde el al menos un pilar de silicio (3) funciona como disipador térmico. 2. Un circuito integrado fotónico híbrido (1) de acuerdo con la reivindicación 1, donde el circuito integrado fotónico híbrido (1) comprende una guía de onda (5) , y donde la guía de onda (5) es una guía de onda (5) de silicio o de nitruro de silicio. 3. Un método para la fabricación de un circuito integrado fotónico híbrido (1) de acuerdo con una cualquiera de las reivindicaciones 1 o 2, donde el método comprende: i. proporcionar una superficie de silicio (2) y, opcionalmente, limpiar la superficie de silicio (2) ; ii. crear al menos un pilar de silicio (3) mediante grabado húmedo o seco de la superficie de silicio (2) ; iii. crear una capa de óxido de silicio (4) mediante oxidación térmica, y pulir la capa de óxido de silicio (4) hasta obtener una primera superficie de confluencia, donde dicha primera superficie de confluencia comprende la base superior del al menos un pilar de silicio (3) y la segunda cara superior de la capa de óxido de silicio (4) ; iv. grabar la capa de óxido de silicio (4) de la primera superficie de confluencia, de manera que se genere una abertura sobre la segunda cara de la capa de óxido de silicio (4) ; v. depositar una guía de onda sobre la primera superficie de confluencia y pulir la guía de onda hasta obtener una segunda superficie de confluencia, donde dicha segunda superficie de confluencia comprende la base superior del al menos un pilar de silicio (3) , la segunda cara de la capa de óxido de silicio (4) , y una superficie de la guía de onda (5) ; vi. disponer la capa de semiconductor III-V (6) sobre la segunda superficie de confluencia, de manera que la capa de semiconductor III-V (6) esté en contacto con la base superior del al menos un pilar de silicio (3) , con la segunda cara de la capa de óxido de silicio (4) , y con la guía de onda (5) . 4. El método de acuerdo con la reivindicación 3, donde la etapa (ii) comprende: ii.a) depositar una capa de nitruro de silicio sobre la superficie de silicio (2) ; ii.b) grabar la capa de nitruro de silicio hasta crear una máscara de nitruro de silicio sobre la superficie de silicio (2) ; ii.c) grabar la superficie de silicio (2) que no está protegida por la máscara de nitruro de silicio de manera que se forme el al menos un pilar de silicio (3) sobre la superficie de silicio (2) . 5. El método de acuerdo con la reivindicación 4, donde el grabado de la etapa (ii.b) es grabado isótropo o grabado anisótropo y/o donde el grabado de la etapa (ii.c) es grabado isótropo. 6. El método de acuerdo con una cualquiera de las reivindicaciones 3 a 5 donde el grabado de la etapa (iv) es grabado seco por plasma mediante la técnica ICP-RIE. 7. El método de acuerdo con una cualquiera de las reivindicaciones 3 a 6, donde la oxidación térmica de la etapa (iii) es oxidación húmeda u oxidación seca. 8. El método de acuerdo con la reivindicación 6, donde la oxidación de la etapa (iii) es oxidación húmeda y donde la oxidación húmeda se lleva a cabo en presencia de vapor a 1100°C durante al menos 12 horas. 9. El método de acuerdo con una cualquiera de las reivindicaciones 3 a 8, donde el pulido de la etapa (iii) y/o de la etapa (v) es pulido mecánico químico.

Los productos y servicios protegidos por este registro son:

H01L 21/02 - H01L 23/34 - H01L 31/024

Descripciones:

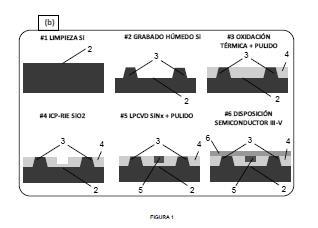

+ ES-2963848_A1 CIRCUITO INTEGRADO FOTÓNICO HÍBRIDO Y MÉTODO DE FABRICACIÓN CAMPO DE LA INVENCIÓN La presente invención se enmarca en el ámbito de la fotónica. Más concretamente, el objeto de la invención se refiere a un circuito integrado fotónico híbrido y a su método de fabricación. ANTECEDENTES DE LA INVENCIÓN La fotónica es una tecnología clave con innumerables aplicaciones que incluyen las comunicaciones ópticas de datos, los sistemas de detección y las tecnologías cuánticas. Estas aplicaciones encuentran usos concretos en industrias como la industria del automóvil (por ejemplo, la conducción autónoma) , aplicaciones biomédicas (dispositivos de laboratorio en un chip) , o aplicaciones en las industrias aeroespacial y de defensa. En este contexto, los circuitos integrados fotónicos híbridos basados en la tecnología del silicio en combinación con la tecnología de los semiconductores III-V son clave para llevar a cabo aplicaciones fotónicas en chips. La combinación de dichas tecnologías generalmente se basa en situar una pieza de un semiconductor III-V sobre la tecnología de silicio. Esta última suele estar compuesta por diferentes materiales dieléctricos depositados sobre una oblea de silicio, de manera que la pieza de semiconductor III-V se asienta sobre los materiales dieléctricos. En la mayoría de las aplicaciones fotónicas, los semiconductores III-V requieren una corriente de polarización para su funcionamiento. Durante la aplicación de dicha corriente de polarización, el semiconductor III-V se calienta, degradando así su rendimiento. Por este motivo, se hace necesario disipar el calor generado para evitar la degradación del rendimiento. Generalmente la vía natural de escape del calor en circuitos integrados fotónicos híbridos es hacia la tecnología de silicio. Sin embargo, los dieléctricos de silicio, como el óxido de silicio y el nitruro de silicio (que son imprescindibles para la funcionalidad fotónica) poseen una baja conductividad térmica. Como solución a este problema, en el estado de la técnica se presentan estructuras que funcionan como disipadores de calor y que están integradas en la arquitectura de los circuitos integrados fotónicos híbridos. Así, Wang et al. ("Optimization and thermal analysis of hybrid microdisk lasers, " 10th International Conference on Group IV Photonics, Seoul, Korea (South) , 2013, pp. 49-50) divulgan un láser de microdisco que incorpora en el centro una estructura de polisilicio como disipador de calor de modo que la capa activa del láser está conectada érmicamente con el sustrato de silicio (buen conductor térmico) . Sin embargo, la estructura del disipador de calor se forma mediante un paso de grabado a través de las capas de semiconductor III-V y de óxido de silicio hasta el sustrato de silicio, para luego formar un disipador de calor de polisilicio mediante deposición y pulido mecánico químico. Esto implica que se crean espacios de discontinuidad en la capa de semiconductor III-V. De manera similar, el documento US 2022/ 0344233 A1 describe estructuras disipadoras de calor que se introducen en la estructura después de procedimientos de grabado a través de las capas de material dieléctrico. Así, existe una necesidad en este campo técnico de proveer soluciones alternativas para la disipación del calor generado en la zona activa de los circuitos integrados fotónicos híbridos. DESCRIPCIÓN DETALLADA DE LA INVENCIÓN En vista de las necesidades en este campo técnico, los inventores han desarrollado un método para la fabricación de un circuito integrado fotónico híbrido (1) donde un semiconductor III-V se dispone sobre un chip de tecnología de silicio que incorpora pilares de silicio alrededor de los materiales dieléctricos (tales como el óxido de silicio y/o el nitruro de silicio) , de tal manera que el flujo térmico para la disipación de calor se produce preferentemente a través de dichos pilares de silicio, ya que el silicio tiene una conductividad térmica un orden de magnitud mayor que los dieléctricos de óxido de silicio y nitruro de silicio. De esta manera, se consigue un funcionamiento más eficiente del dispositivo. El método desarrollado por los inventores tiene la ventaja adicional de que no se necesita grabar a través de la capa de semiconductor III-V para la integración de la estructura disipadora de calor, por lo que dicha capa de semiconductor III-V se mantiene intacta. Así, la invención se refiere en un primer aspecto a un circuito integrado fotónico híbrido (1) que comprende: a) una capa funcional fotónica de tecnología de silicio que comprende: - una superficie de silicio (2) , donde la superficie de silicio (2) comprende al menos un pilar de silicio (3) , donde el al menos un pilar de silicio (3) tiene dos bases, una base inferior y una base superior, donde la base inferior está dispuesta sobre la superficie de silicio (2) , y donde la superficie de silicio (2) y el al menos un pilar de silicio (3) forman, sin interrupción, una única pieza; - una capa de óxido de silicio (4) , donde la capa de óxido de silicio (4) comprende dos caras, una primera cara y una segunda cara, donde la primera cara está ispuesta sobre la superficie de silicio (2) , y donde la capa de óxido de silicio (4) está atravesada por el al menos un pilar de silicio (3) entre la primera cara y la segunda cara; - opcionalmente, una guía de onda (5) , donde la guía de onda (5) está comprendida en la capa de óxido de silicio (4) , y donde la guía de onda (5) no está en contacto directo ni con la superficie de silicio (2) ni con el al menos un pilar de silicio (3) ; y b) una capa de un semiconductor III-V (6) o un chip que se pueda hibridar con una tecnología de dieléctricos de silicio, donde la capa de semiconductor III-V (6) o el chip que se pueda hibridar con una tecnología de dieléctricos de silicio está en contacto con la base superior del al menos un pilar de silicio (3) , con la segunda cara de la capa de óxido de silicio (4) , y opcionalmente con la guía de onda (5) , y donde la capa de semiconductor III-V (6) o el chip que se pueda hibridar con una tecnología de dieléctricos de silicio no está atravesada por el al menos un pilar de silicio (3) , donde el al menos un pilar de silicio (3) funciona como disipador térmico. En el contexto de la invención, el término "circuito integrado fotónico" (o PIC, del inglés "photonic integrated circuit", también llamado circuito óptico integrado) se refiere a un microchip que detecta, genera, transporta y/o procesa luz ya que comprende un circuito funcional que contiene más de un componente fotónico. Así, en un chip fotónico, los fotones del haz de luz pasan a través de componentes ópticos como guías de ondas (equivalentes a una resistencia o cable eléctrico) , láseres (equivalentes a transistores) , polarizadores y desfasadores. Un chip puede integrar diferentes tecnologías con propiedades ópticas diversas de tal manera que se obtenga un circuito híbrido. Así, una plataforma híbrida puede integrar de forma heterogénea la funcionalidad de un semiconductor III/V en una plataforma de tecnología de silicio. En el contexto de la invención, el término "tecnología de silicio" se refiere a los sistemas fotónicos basados en silicio y derivados de silicio con los que se pueden fabricar varios elementos estructurales con diferentes capacidades funcionales. Por ejemplo, el silicio y el nitruro de silicio pueden funcionar como guías de onda, mientras que el óxido de silicio puede funcionar como un elemento aislante. Para la microfabricación de elementos de la tecnología de silicio se debe partir inicialmente de una superficie de silicio (2) . En el contexto de la presente invención, el término "superficie de silicio" se refiere a una cara superficial de una capa de silicio, donde la capa de silicio se refiere típicamente a una lámina constituida por el material semiconductor silicio cristalino de alta pureza. En el campo de la microelectrónica, las láminas de materiales semiconductores se suelen proporcionar en forma de obleas (o por el término en inglés, "wafer") y generalmente se emplean para la fabricación de microcircuitos mediante técnicas de dopado, grabado químico y deposición de varios ateriales. Por ello, en la presente invención el término "capa de silicio" también puede entenderse como "oblea de silicio" o "wafer de silicio" si se emplea la terminología inglesa. Otro término equivalente a "capa de silicio", "oblea de silicio" o "wafer de silicio" es "sustrato de silicio", dado que, para la síntesis de los microcircuitos, la capa de silicio actúa como sustrato, sobre el cual se van depositando el resto de capas constituidas por distintos materiales. Generalmente, a nivel microscópico, la lámina de material semiconductor silicio cristalino puede presentar un espesor del rango de centenas de micrómetros. Por ejemplo, una oblea de silicio de 4 puede tener un espesor de 525 ^m, mientras que una oblea de 6 puede tener un espesor de unos 675 ^m. En modos de realización de la invención, la oblea de silicio tiene una orientación (111) , una orientación (100) , o una orientación (110) . El objeto de la presente invención es la fabricación de al menos un pilar de silicio (3) como elemento estructural dentro de un circuito integrado fotónico híbrido (1) con la función de actuar como elemento disipador de calor desde la zona activa del dispositivo hacia el sustrato de silicio. En este sentido, el al menos un pilar de silicio (3) de la presente invención permite poner en contacto térmico la zona activa de la invención (por ejemplo, la capa de material semiconductor III-V) con el sustrato de silicio. En el contexto de la invención, el término "disipador térmico" o "disipador de calor" se refiere a un elemento estructural integrado en el dispositivo que permite y facilita la transferencia de flujos de calor a través del mismo. Dicha capacidad de transferencia de calor viene dada por el diseño del dispositivo, concretamente por los materiales que lo conforman y la disposición de los mismos. En modos particulares de realización de la presente invención, el circuito integrado fotónico comprende al menos uno, al menos dos, al menos tres, al menos cuatro, al menos cinco, al menos diez, al menos veinte, al menos treinta, al menos cuarenta, al menos cincuenta, al menos cien, al menos doscientos, al menos quinientos, al menos mil, al menos dos mil, al menos cinco mil, al menos diez mil pilares de silicio. Así, en modos particulares de realización de la presente invención, el circuito integrado fotónico comprende 1, 2, 3, 4, 5, 6, 10, 12, 15, 20, 30, 40, 50, 60, 70, 80, 90, 100, 120, 150, 200, 250, 500, 750, 1000, 2000, 3000, 4000, 5000, o 10000 pilares de silicio. En el contexto de la invención, el pilar de silicio (3) se puede fabricar en varias formas geométricas que son compatibles con el objeto de la presente invención de disipar calor. Así, en modos particulares de realización de la presente invención, el pilar de silicio (3) puede tener cualquiera de las formas que resulten de la fabricación de dichos pilares (i.e., las formas que resultan del ataque húmedo o seco de silicio cristalino) , independientemente de la orientación cristalina que tenga la oblea de silicio. Estas formas pueden comprender, aunque no se limita a, forma de cubo, forma de ortoedro, forma de prisma triangular, forma de prisma rectangular, forma de prisma pentagonal, forma de cilindro, forma troncocónica, o forma de tronco de irámide. En algunos modos de realización, todos los pilares de silicio del dispositivo de la invención tienen la misma forma geométrica. En otros modos de realización, los pilares de silicio del dispositivo pueden combinar varias formas geométricas distintas. De manera ventajosa, el al menos un pilar de silicio (3) de la presente invención tiene dos bases, una base superior y una base inferior. La base superior está en contacto con la zona activa (por ejemplo, semiconductor III-V) , mientras que la base inferior está en contacto con la superficie de silicio (2) . En la presente invención, la superficie de silicio (2) y el al menos un pilar de silicio (3) forman, sin interrupción, una única pieza única. Es decir, la superficie de silicio (2) y el al menos un pilar de silicio (3) se obtienen por fabricación de un único sustrato común, de tal manera que no hay una interfaz de unión entre la base inferior y la superficie de silicio (2) como tal, sino que ambos elementos estructurales forman una única pieza. Es decir, como resultado de la fabricación del pilar de silicio (3) sobre el mismo sustrato de la superficie de silicio (2) , el al menos un pilar de silicio (3) conforma un cuerpo solidario con la superficie de silicio (2) . En el contexto de la invención, el término "guía de onda", en particular una guía de onda óptica se refiere a una estructura física que permite la conducción de ondas electromagnéticas en el espectro óptico. De manera general, las guías de onda ópticas pueden ser una fibra óptica, guías de ondas dieléctricas transparentes hechas de plástico y/o vidrio, y guías de ondas líquidas. En el contexto de los circuitos integrados fotónicos, las guías de onda óptica se usan como componentes para permitir la transmisión de luz en sistemas de comunicación óptica a escala local o a larga distancia. Las guías de ondas ópticas se pueden clasificar según su geometría (guías de ondas planas, de tira o de fibra) , estructura de modo (monomodo, multimodo) , distribución del índice de refracción (índice de paso o gradiente) y material (vidrio, polímero, semiconductor) . En relación con la presente invención, la guía de onda (5) está integrada en el dispositivo (i.e., en el circuito integrado fotónico híbrido (1) ) , de tal manera que está embebida en la capa de óxido de silicio (4) , y opcionalmente puede estar fabricada en silicio y/o en nitruro de silicio. El óxido de silicio (SiO2) , se utiliza en el contexto de la presente invención por sus propiedades como dieléctrico, donde el SiO2 es aislante eléctrico y mal conductor térmico. El óxido de silicio se utiliza también para aislar ópticamente las guías de onda integradas en el dispositivo óptico de la presente invención. En este sentido, el óxido de silicio encapsula el núcleo de la guía de onda (nitruro de silicio o silicio) . Dado que el índice de refracción del óxido de silicio (1.45 a longitud de onda de 1.55 ^m) es menor que el del núcleo (2.0 y 3.45 parar nitruro de silicio y silicio respectivamente) , se guía la luz por la estructura combinada, debido a la presencia de ese material de índice mayor. En la presente invención, la capa de óxido de silicio (4) comprende dos caras, una primera cara y una egunda cara. La capa de óxido de silicio (4) está atravesada por el al menos un pilar de silicio (3) entre la primera cara y la segunda cara La primera cara está dispuesta sobre la superficie de silicio (2) , mientras que la segunda cara está en contacto con el semiconductor III-V. La capa de óxido de silicio (4) tiene embebida la o las guías de onda del dispositivo de la invención. El experto en la materia puede entender que existen métodos sobradamente conocidos en el estado de la técnica para la preparación de una abertura en la segunda cara de la capa de óxido de silicio (4) , de tal manera que se pueda disponer una guía de onda (5) en dicha abertura de la segunda cara de la capa de óxido de silicio (4) . En una realización particular de la invención, la guía de onda (5) está fabricada en silicio o en nitruro de silicio. Por otra parte, el nitruro de silicio (Si3N4 , SiNx , o SiN) es un material cerámico que presenta alta dureza y resistencia. En el campo de la microelectrónica, el nitruro de silicio se utiliza para diversos fines como material dieléctrico, capas de pasivación, máscaras duras, como guía de onda (5) o como una combinación de estos. En el contexto de la presente invención, la guía de onda (5) (por ejemplo, la guía de onda (5) de silicio o nitruro de silicio) no está en contacto directo ni con la superficie de silicio (2) ni con el al menos un pilar de silicio (3) . En el contexto de la invención, debe haber una distancia mínima efectiva entre la guía de onda (sea esta de nitruro de silicio o de silicio) y el pilar de silicio, de tal manera que el haz de luz en el interior de la guía de onda no tenga tendencia a irse hacia el pilar de silicio. El experto en la materia puede determinar a qué distancia mínima debe disponerse la guía de onda (5) con respecto al pilar de silicio (3) , de manera que la transmisión de luz no se vea alterada. Para ello, el experto en la materia puede resolver las ecuaciones de Maxwell en la sección cruzada. Generalmente estas ecuaciones se resuelven mediante métodos numéricos computacionales, de manera que se determinan los modos de propagación en la guía de onda (5) . En concreto, la distancia mínima de la guía de onda (5) se fijará tomando como criterio que la parte imaginaria del índice efectivo de propagación de los modos sea suficientemente pequeña para una determinada aplicación, siendo del orden de 10-18 en el caso de materiales ideales sin pérdidas, considerándose este valor como nulo (suelo numérico del cálculo) . En el contexto de la presente invención, un semiconductor III-V son materiales compuestos por uno o más elementos de la columna III (boro, galio, aluminio, indio, etc.) y de la columna V (arsénico, antimonio, fósforo, etc.) de la tabla periódica de Mendeléyev, que se corresponden con los grupos 13 y 15, respectivamente, en la tabla periódica moderna. En modos particulares de realización, el semiconductor III-V se selecciona del grupo que consiste en antimoniuro de aluminio, antimoniuro de galio, antimoniuro de indio, arseniuro de aluminio, arseniuro de aluminio y galio, arseniuro de aluminio e indio, arseniuro de boro, arseniuro de galio, arseniuro de galio e indio, arseniuro de indio, fosfo-antimoniuro arseniuro de galio e ndio, fosfo-antimoniuro arseniuro de indio, fosfo-arseniuro de galio, fosfo-arseniuro de galio e indio, fosfuro de aluminio, fosfuro de aluminio y galio, fosfuro de aluminio, galio e indio, fosfuro de boro, fosfuro de galio, fosfuro de galio e indio, fosfuro de indio, nitruro de aluminio, nitruro de aluminio y galio, nitruro de aluminio, galio e indio, nitruro de aluminio e indio, nitruro de boro, nitruro de galio, nitruro de galio e indio, nitruro de indio, y combinaciones de los mismos. En el contexto de la invención, el semiconductor III-V se dispone después de que se haya fabricado el al menos un pilar de silicio (3) como estructura disipadora térmica, de tal manera que el semiconductor III-V está integrado en el circuito integrado fotónico híbrido (1) como una capa intacta en el sentido de que no está atravesada por el al menos un pilar de silicio (3) . En cualquier caso, son posibles modificaciones posteriores de la capa de semiconductor III-V (6) . En el contexto de la invención, el semiconductor III-V que se dispone puede estar comprendido bien por un semiconductor III-V que se ha crecido "in-situ" sobre la base superior del al menos un pilar de silicio (3) , la segunda cara de la capa de óxido de silicio (4) , y la guía de onda (5) , o por un semiconductor III-V que previamente se ha fabricado separadamente y que posteriormente se dispone sobre la base superior del al menos un pilar de silicio (3) , la segunda cara de la capa de óxido de silicio (4) , y la guía de onda (5) ) . La presente invención contempla también sistemas híbridos que comprenden, en lugar de un semiconductor III-V, un chip que se pueda hibridar con una tecnología de dieléctricos de silicio, de tal manera que todo aquel chip que se pueda colocar encima de una tecnología de dieléctricos de silicio (y que genere calor) podría aprovechar esta invención de pilares de silicio como estructuras de disipación de calor y de reducción de barrera térmica entre el dispositivo que se calienta y la oblea de silicio. En un segundo aspecto, la invención se refiere a un método para la fabricación de un circuito integrado fotónico híbrido (1) de acuerdo con la reivindicación 1, donde el método comprende: i. proporcionar una superficie de silicio (2) y, opcionalmente, limpiar la superficie de silicio (2) ; ii. crear al menos un pilar de silicio (3) mediante grabado húmedo o seco de la superficie de silicio (2) ; iii. crear una capa de óxido de silicio (4) mediante oxidación térmica, y pulir la capa de óxido de silicio (4) hasta obtener una primera superficie de confluencia, donde dicha primera superficie de confluencia comprende la base superior del al menos un pilar de silicio (3) y la segunda cara superior de la capa de óxido de silicio (4) ; iv. grabar la capa de óxido de silicio (4) de la primera superficie de confluencia, de manera que se genere una abertura sobre la segunda cara de la capa de óxido de silicio (4) ; . depositar una guía de onda sobre la primera superficie de confluencia y pulir la guía de onda hasta obtener una segunda superficie de confluencia, donde dicha segunda superficie de confluencia comprende la base superior del al menos un pilar de silicio (3) , la segunda cara de la capa de óxido de silicio (4) , y una superficie de la guía de onda (5) ; vi. disponer la capa de semiconductor III-V (6) sobre la segunda superficie de confluencia, de manera que la capa de semiconductor III-V (6) esté en contacto con la base superior del al menos un pilar de silicio (3) , con la segunda cara de la capa de óxido de silicio (4) , y con la guía de onda (5) . La etapa (i) del método de la invención comienza con la provisión de una superficie de silicio (2) , donde la superficie de silicio (2) debe estar perfectamente limpia para poder llevar a cabo los procedimientos microfabricación de la invención. Por este motivo, puede ser necesario llevar a cabo el método de la presente invención en una sala blanca (también llamado cuarto limpio o sala limpia; en inglés, "clean room") . De manera opcional, el método provee una etapa para limpiar la superficie de silicio (2) a través de métodos sobradamente conocidos en el estado de la técnica. En un modo de realización de la invención, la etapa opcional de limpieza de la superficie de silicio (2) se lleva a cabo por grabado húmedo o grabado seco, de modo isótropo o anisótropo. Tal y como se usa en el contexto de la presente invención, el grabado o también conocido por su terminología en inglés "etching" puede realizarse de diversas maneras, modificando la dirección de aplicación y la naturaleza de los agentes empleados para el grabado. Según la dirección de aplicación, el grabado puede ser isótropo o anisótropo y según la naturaleza de los agentes empleados, puede ser grabado seco o húmedo. En función del grabado que se lleve a cabo, el procedimiento a seguir es uno u otro y de ello dependerá la morfología de la superficie donde se aplique el grabado. El grabado isótropo retira el material de manera uniforme en todas las direcciones, por ello, con este grabado generalmente se obtienen superficies lisas. Sin embargo, el grabado anisótropo elimina el material a lo largo de planos cristalográficos específicos produciendo así perfiles concretos como esquinas o bordes afilados y superficies que presentan rugosidades debido a la exposición cristalográfica. El grabado húmedo o también conocido como grabado químico o líquido consiste en la eliminación del material mediante el uso de sustancias químicas. De manera que aquellos materiales que no estén protegidos por las máscaras depositadas tras una etapa previa de litografía serán eliminados por las sustancias químicas. En modos particulares de la invención, las sustancias químicas utilizadas para eliminar el material consisten en disoluciones de idróxido de potasio y/o de hidróxido de tetrametilamonio. Este tipo de grabado implica reacciones químicas donde la sustancia química difunde en el material a retirar, reaccionando ambos entre sí, dando como resultado la difusión de los subproductos de la reacción desde la superficie reaccionada. En cambio, en el grabado en seco, el material se retira mediante plasma o agentes gaseosos. En todos ellos se produce una reacción, la cual tiene lugar mediante el uso de energía cinética procedente de haces de partículas, reacciones químicas o la combinación de ambos. El grabado físico requiere de haces de alta energía cinética (iones, electrones o fotones) para eliminar átomos de la superficie. El grabado químico o también conocido como grabado en fase de vapor no utiliza sustancias químicas, en este caso se utilizan gases que ataquen la superficie. Dentro del grabado que combina los fenómenos físicos y químicos destaca el grabado de iones reactivos (RIE) . Al combinar ambos fenómenos se consigue una mayor resolución y el tiempo requerido para ello es menor en comparación con los demás tipos de grabados. La técnica de grabado de iones reactivos (RIE) se puede implementar junto con la técnica de plasma acoplado inductivamente (ICP) . En el campo de la invención ICP-RIE se refiere al proceso de grabado en el cual se hace uso de una fuente de plasma acoplada inductivamente. Con este proceso, los materiales se graban con el uso de un plasma químicamente reactivo en condiciones de baja presión, combinándolo con el grabado inducido por iones. En un modo de realización, el grabado de la etapa (ii.b) del método de la invención es grabado isótropo o grabado anisótropo. En un modo de realización, el grabado de la etapa (ii.c) es grabado isótropo. En este último caso, el experto en la materia conoce que, en determinadas situaciones experimentales, un grabado isótropo mediante ataque húmedo puede resultar esencialmente anisótropo en sustratos como el silicio, ya que algunos químicos (por ej., KOH) atacan en un modo distinto según la dirección del cristal. En un modo de realización, el grabado de la etapa (iv) del método de la invención es grabado seco por plasma mediante la técnica ICP-RIE. En el contexto de la invención "litografía" o "fotolitografía" se refiere a un proceso comúnmente empleado en la fabricación de dispositivos semiconductores o circuitos integrados, donde se transfiere el patrón de un diseño de manera directa o mediante una máscara (o fotomáscara) a una superficie. La máscara puede estar preparada en una variedad de materiales, tales como máscaras rígidas metálicas, películas de acetato transparente impresas, etcétera. Las fotomáscaras también pueden ser impresas directamente sobre la superficie a tratar, si el material de recubrimiento necesita tener propiedades especiales. En estos casos, el patrón de una fotomáscara primaria se puede transferir a una capa de material fotoresistente (positiva o negativa) para producir una máscara secundaria. Esta máscara secundaria de material fotoresistente (en inglés, photoresist) se puede utilizar para grabar el patrón en el material ubyacente y que sea este el que finalmente se use como máscara de protección en un último paso de grabado de la capa de material de interés. Este sería el caso, por ejemplo, de la transferencia del patrón de la máscara inicial a una máscara de nitruro de silicio para grabar una superficie de silicio (2) . En el contexto de la invención "grabado" se refiere al proceso utilizado para eliminar determinadas capas de material de una superficie durante la fabricación del dispositivo. Las técnicas de litografía son sobradamente conocidas para un experto en la materia para poner en práctica este aspecto de la invención (Sharma E, et al., Evolution in Lithography Techniques: Microlithography to Nanolithography, Nanomaterials (Basel) , 2022 Aug 11;12 (16) :2754) . En el contexto de la invención, el término "oxidación térmica" se refiere a un proceso utilizado comúnmente en microfabricación para obtener una capa de óxido en el diseño del dispositivo. Así, en el contexto de la invención, la "oxidación térmica" se refiere al tratamiento por el cual se crece óxido de silicio a expensas de la superficie de silicio (2) . La oxidación térmica puede ser húmeda o seca, donde la oxidación húmeda se lleva a cabo en presencia de vapor de agua a una temperatura de 800-1200°C, mientras que la oxidación seca se realiza con oxígeno puro a una temperatura de unos 1200°C. En el caso del silicio, la oxidación húmeda y la oxidación seca se realizan respectivamente de acuerdo con las ecuaciones (1) y (2) : (1) Si + 2H2O SiO2 + 2H2 (2) Si + O2 SiO2 En un modo de realización, la oxidación térmica de la etapa (iii) del método de la invención es oxidación húmeda u oxidación seca. En modos de realización de la invención, la oxidación de la etapa (iii) del método de la invención es oxidación húmeda (i.e., en presencia de vapor de agua) , donde la oxidación húmeda se lleva a cabo a una temperatura de entre 800-1200°C. En modos particulares de realización, la oxidación húmeda se lleva a cabo a 800°C, 850°C, 900°C, 950°C, 1000°C, 1050°C, 1100°C, 1150°C, o 1200°C. En modos de realización de la invención, la oxidación húmeda se lleva a cabo durante al menos 1, 2, 3, 4, 5, 8, 10, 12, o 15 horas. En un modo de realización particular, la oxidación húmeda se lleva a cabo a 1100°C durante al menos 12 horas. En el contexto de la invención, el término "depositar" o "deposición" se refiere a una etapa de recubrimiento de un sustrato con algún tipo de material. La deposición se puede referir a un recubrimiento por rotación capaz de depositar una capa fotorresistente sobre un sustrato, como pueda ser una oblea de silicio. En modos de realización de la invención, la etapa de deposición puede ser deposición química de vapor (CVD) . En modos particulares de ealización, la deposición se puede seleccionar del grupo que consiste en deposición química de vapor mejorada con plasma (PECVD) , deposición química de vapor a baja presión (LPCVD) , deposición química de vapor de plasma de alta densidad (HDP-CVD) , deposición química de vapor subatmosférica (SACVD) , deposición de capas atómicas (ALD) , deposición de capas atómicas mejorada por plasma (PEALD) y combinaciones de los mismos. En modos particulares de realización de la invención, la etapa de deposición puede ser una etapa de deposición física de vapor (PVD) , como por ejemplo pulverización catódica. La elección del método de deposición vendrá determinada por el material que se pretende depositar. En el campo de la invención, el "pulido mecánico químico" o "planarización mecánica química" se refiere a un proceso de alisado de superficies mediante la acción de fuerzas mecánicas y químicas donde se realizan simultáneamente un grabado químico ("chemical etching") y un pulido abrasivo. En un modo de realización, el pulido de la etapa (iii) y/o el pulido de la etapa (v) del método de la invención es pulido mecánico químico. En un modo de realización, la etapa (ii) del método de la invención comprende: ii.a) depositar una capa de nitruro de silicio sobre la superficie de silicio (2) ; ii.b) grabar la capa de nitruro de silicio hasta crear una máscara de nitruro de silicio sobre la superficie de silicio (2) ; ii.c) grabar la superficie de silicio (2) que no está protegida por la máscara de nitruro de silicio de manera que se forme el al menos un pilar de silicio (3) sobre la superficie de silicio (2) . Así, en un modo de realización de la invención, el grabado sobre la superficie de silicio (2) para formar los pilares de silicio se realiza a través de una máscara dura de nitruro de silicio. En este paso del procedimiento, una vez que se ha grabado la superficie de silicio (2) , la máscara de nitruro de silicio permanece depositada sobre la base superior de los pilares de silicio. Por este motivo, es necesario que durante la etapa posterior de pulido mecánico químico (parte de la etapa (iii) en el método de la invención) se elimine completamente dicha máscara dura de nitruro de silicio depositada sobre la base superior de los pilares de silicio. Todos los términos y modos de realización descritos anteriormente son aplicables a cualquier aspecto y modo de realización de la invención. De acuerdo con la presente invención, el término en singular "el", "la", "un", "uno", "una", se refiere igualmente a su correspondiente en plural "los", "las", "unos", "unas", salvo que se desprenda del contexto que claramente el término se refiere a una especie en el singular. El término "comprende" o "que comprende", al y como se usa en el presente documento, también describe "consiste en" o "que consiste en" de acuerdo con la práctica de patentes generalmente aceptada. EJEMPLOS La siguiente invención se describe por medio de los siguientes ejemplos, que deben interpretarse como meramente ilustrativos y no limitativos del alcance de la invención. Ejemplo 1: Proceso para la preparación de un circuito integrado fotónico híbrido con disipador de calor Los inventores han diseñado un procedimiento para la preparación de un circuito integrado fotónico híbrido, donde el circuito presenta unos pilares de silicio que actúan como una estructura disipadora de calor. En este procedimiento, los pilares se crean esencialmente con una combinación de grabado húmedo de silicio, seguido de oxidación térmica y pulido químico mecánico. El procedimiento tiene las etapas que se muestran en la figura 1, donde se comparan con las etapas típicas de la preparación de un circuito integrado fotónico híbrido que no incluye un disipador de calor. Así, el panel (a) de la figura 1 muestra un procedimiento de preparación de un circuito integrado fotónico híbrido que no incluye un disipador de calor, donde las etapas son: #1. Limpieza de la superficie de silicio por grabado húmedo. #2. Oxidación húmeda de la superficie de silicio para obtener una capa superficial de óxido de silicio. #3. Deposición de una capa de nitruro de silicio por deposición química de vapor a baja presión (LPCVD por sus siglas del inglés "Low pressure chemical vapor deposition") . #4. Litografía de una máscara con el circuito de interés para una guía de onda, seguida de grabado en seco de la superficie de nitruro de silicio mediante grabado de iones reactivos de plasma acoplado inductivo (ICP-RIE por sus siglas del inglés "inductively coupled plasma, reactive-ion etching") . #5. Deposición de una capa de óxido de silicio por deposición química de vapor potenciada por plasma (PECVD por sus siglas del inglés "plasma enhanced chemical vapour deposition") , seguida de pulido mecánico químico. #6. Disposición de una capa de semiconductor III-V. Por otra parte, el panel (b) de la figura 1 muestra un procedimiento de preparación de un circuito integrado fotónico híbrido con disipador de calor, donde las etapas son: #1. Limpieza de la superficie de silicio por grabado húmedo. #2. Litografía de una máscara con el diseño bidimensional en superficie de la estructura que funcionará como disipador de calor (i.e., pilares de silicio) , seguida de grabado húmedo de la superficie de silicio en las partes no protegidas por la máscara para producir dicha estructura en tres dimensiones. #3. Oxidación húmeda de la superficie de silicio para obtener una capa superficial de óxido de silicio, seguida de pulido mecánico químico hasta dejar al descubierto una superficie de silicio (correspondiente a los pilares de silicio) y una superficie de óxido de silicio. #4. Litografía de una máscara con el circuito de interés para una guía de onda, seguida de grabado en seco de la superficie de óxido de silicio mediante grabado de iones reactivos de plasma acoplado inductivo (ICP-RIE por sus siglas del inglés "inductively coupled plasma, reactive-ion etching") . #5. Deposición de una capa de nitruro de silicio por deposición química de vapor a baja presión (LPCVD por sus siglas del inglés "Low pressure chemical vapor deposition") , seguida de pulido mecánico químico hasta dejar al descubierto una superficie de silicio (correspondiente a los pilares de silicio) , una superficie de óxido de silicio y una superficie de nitruro de silicio (correspondiente a una guía de onda de nitruro de silicio) . #6. Disposición de una capa de semiconductor III-V. En el panel (c) de la figura 1 se muestra la conducción de calor en una sección transversal del circuito integrado fotónico híbrido resultante de cada uno de los procedimientos, donde en ambos casos se coloca una fuente de calor sobre la superficie superior (de la capa de semiconductor III-V) . Se puede apreciar que el calor en la sección transversal del circuito resultante del procedimiento (a) se transmite directamente a los materiales dieléctricos de la tecnología de silicio (es decir, óxido de silicio y nitruro de silicio) que tienen una conductividad térmica relativamente baja, mientras que el calor en la sección transversal del circuito resultante del procedimiento (b) sigue un flujo de calor a través de un recorrido a través de los pilares de silicio, que tienen una conductividad térmica comparativamente mayor. La viabilidad del proceso de fabricación se ha simulado con una de las mejores herramientas de simulación de procesos de semiconductores del mercado (Sentaurus Process, de Synopsys) . Los resultados de la simulación de flujo se muestran en la figura 2. #1. Limpieza de la superficie de silicio por grabado húmedo. #2a. Deposición de una capa de nitruro de silicio. #2b. Litografía sobre la capa de nitruro de silicio de una máscara con el diseño bidimensional en superficie de la estructura que funcionará como disipador de calor (i.e., pilares de silicio) , seguida de grabado (isótropo o anisótropo) de la capa de nitruro de silicio en las partes no protegidas por la máscara, de tal manera que se produce una máscara de nitruro de silicio. #2c. Grabado húmedo (isótropo) de la superficie de silicio en las partes no protegidas por la máscara de nitruro de silicio para producir la estructura de los pilares de silicio en tres dimensiones. #3a. Oxidación térmica húmeda de la superficie de silicio para obtener una capa superficial de óxido de silicio, a una temperatura de 1100°C durante 20 minutos en presencia de vapor de agua. #3b. Pulido mecánico químico hasta dejar al descubierto una superficie de silicio (correspondiente a los pilares de silicio) y una superficie de óxido de silicio. #4. Litografía de una máscara con el circuito de interés para una guía de onda, seguida de grabado en seco de la superficie de óxido de silicio mediante grabado de iones reactivos de plasma acoplado inductivo (ICP-RIE por sus siglas del inglés "inductively coupled plasma, reactive-ion etching") . #5. Deposición de una capa de nitruro de silicio por deposición química de vapor a baja presión (LPCVD por sus siglas del inglés "Low pressure chemical vapor deposition") , seguida de pulido mecánico químico hasta dejar al descubierto una superficie de silicio (correspondiente a los pilares de silicio) , una superficie de óxido de silicio y una superficie de nitruro de silicio (correspondiente a una guía de onda de nitruro de silicio) . #6. Disposición de una capa de semiconductor III-V. Tal y como se aprecia en la descripción de etapas en la figura 2, la creación de los pilares de silicio ocurre con la combinación de las etapas #2 y #3. Hay que tener en cuenta que el dióxido de silicio crece en ambos lados de la interfaz de silicio inicial cuando se oxida el silicio. Así, el óxido crece hasta un espesor determinado dependiendo del tiempo de oxidación, donde el óxido recién creado está un 46% por debajo de la posición de la superficie original de silicio y un 54% por encima de la misma. El enmascaramiento de nitruro de silicio en la etapa #2c evita que el pilar de silicio creado se oxide desde la parte superior. Esto se puede observar en la etapa #3a, donde se ve que el dióxido de silicio crece a expensas del silicio tanto verticalmente como dentro del pilar; y se aprecia la dimensión lateral reducida del pilar, comparativamente entre las etapas #2c y #3a. Por otra parte, la figura 3 corresponde con micrografías obtenidas mediante microscopio electrónico de barrido durante el procedimiento de preparación de un circuito integrado fotónico hibrido con disipador de calor. Concretamente, en estas micrografías se muestra el resultado obtenido a nivel microscópico tras llevar a cabo la combinación de las etapas #2c y #3a del flujo de proceso de la figura 1 (b) . DESCRIPCIÓN DE LAS FIGURAS Figura 1: (a) Flujo de proceso para la preparación de una plataforma de guía de ondas comúnmente utilizada sin estructuras de disipador de calor. (b) Flujo de proceso para la preparación de una plataforma de guía de ondas pilares de silicio. (c) Sección transversal final de ambas tecnologías, con una fuente de calor en la parte superior, que indica las rutas preferidas de flujo de calor. Figura 2: Explicación detallada desde la etapa 1 a la etapa 5 en el flujo de proceso de la figura 1 (b) . Figura 3: Explicación detallada desde la etapa 2 a la 3 en el flujo de proceso de la figura 1 (b) . REFERENCIAS NUMÉRICAS UTILIZADAS EN LAS FIGURAS Con objeto de ayudar a una mejor comprensión de las características técnicas de la invención, las citadas figuras se acompañan de una serie de referencias numéricas donde, con carácter ilustrativo y no limitativo, se representa lo siguiente:

Publicaciones:

ES2963848 (02/04/2024) - A1 Solicitud de patente con informe sobre el estado de la técnica

Eventos:

En fecha 16/02/2024 se realizó Registro Instancia de Solicitud

En fecha 19/02/2024 se realizó Admisión a Trámite

En fecha 19/02/2024 se realizó Aceptación Tramitación CAP

En fecha 19/02/2024 se realizó 1001P_Comunicación Admisión a Trámite

En fecha 19/02/2024 se realizó Superado examen de oficio

En fecha 18/03/2024 se realizó Realizado IET

En fecha 21/03/2024 se realizó 1109P_Comunicación Traslado del IET

En fecha 02/04/2024 se realizó Publicación Solicitud

En fecha 02/04/2024 se realizó Publicación Folleto Solicitud con IET (A1)

En fecha 23/04/2024 se realizó 5215P_Observaciones del solicitante al IET, Opinión Escrita y/o alegaciones a observaciones de terceros

Pagos:

16/02/2024 - Pago Tasas IET

+ ES-2963848_A11. Un circuito integrado fotónico híbrido (1) que comprende: a) una capa funcional fotónica de tecnología de silicio que comprende: - una superficie de silicio (2) , donde la superficie de silicio (2) comprende al menos un pilar de silicio (3) , donde el al menos un pilar de silicio (3) tiene dos bases, una base inferior y una base superior, donde la base inferior está dispuesta sobre la superficie de silicio (2) , y donde la superficie de silicio (2) y el al menos un pilar de silicio (3) forman, sin interrupción, una única pieza; - una capa de óxido de silicio (4) , donde la capa de óxido de silicio (4) comprende dos caras, una primera cara y una segunda cara, donde la primera cara está dispuesta sobre la superficie de silicio (2) , y donde la capa de óxido de silicio (4) está atravesada por el al menos un pilar de silicio (3) entre la primera cara y la segunda cara; - opcionalmente, una guía de onda (5) , donde la guía de onda (5) está comprendida en la capa de óxido de silicio (4) , y donde la guía de onda (5) no está en contacto directo ni con la superficie de silicio (2) ni con el al menos un pilar de silicio (3) ; y b) una capa de un semiconductor III-V (6) o un chip que se pueda hibridar con una tecnología de dieléctricos de silicio, donde la capa de semiconductor III-V (6) o el chip que se pueda hibridar con una tecnología de dieléctricos de silicio está en contacto con la base superior del al menos un pilar de silicio (3) , con la segunda cara de la capa de óxido de silicio (4) , y opcionalmente con la guía de onda (5) , y donde la capa de semiconductor III-V (6) o el chip que se pueda hibridar con una tecnología de dieléctricos de silicio no está atravesada por el al menos un pilar de silicio (3) , donde el al menos un pilar de silicio (3) funciona como disipador térmico. 2. Un circuito integrado fotónico híbrido (1) de acuerdo con la reivindicación 1, donde el circuito integrado fotónico híbrido (1) comprende una guía de onda (5) , y donde la guía de onda (5) es una guía de onda (5) de silicio o de nitruro de silicio. 3. Un método para la fabricación de un circuito integrado fotónico híbrido (1) de acuerdo con una cualquiera de las reivindicaciones 1 o 2, donde el método comprende: i. proporcionar una superficie de silicio (2) y, opcionalmente, limpiar la superficie de silicio (2) ; ii. crear al menos un pilar de silicio (3) mediante grabado húmedo o seco de la superficie de silicio (2) ; iii. crear una capa de óxido de silicio (4) mediante oxidación térmica, y pulir la capa de óxido de silicio (4) hasta obtener una primera superficie de confluencia, donde dicha primera superficie de confluencia comprende la base superior del al menos un pilar de silicio (3) y la segunda cara superior de la capa de óxido de silicio (4) ; iv. grabar la capa de óxido de silicio (4) de la primera superficie de confluencia, de manera que se genere una abertura sobre la segunda cara de la capa de óxido de silicio (4) ; v. depositar una guía de onda sobre la primera superficie de confluencia y pulir la guía de onda hasta obtener una segunda superficie de confluencia, donde dicha segunda superficie de confluencia comprende la base superior del al menos un pilar de silicio (3) , la segunda cara de la capa de óxido de silicio (4) , y una superficie de la guía de onda (5) ; vi. disponer la capa de semiconductor III-V (6) sobre la segunda superficie de confluencia, de manera que la capa de semiconductor III-V (6) esté en contacto con la base superior del al menos un pilar de silicio (3) , con la segunda cara de la capa de óxido de silicio (4) , y con la guía de onda (5) . 4. El método de acuerdo con la reivindicación 3, donde la etapa (ii) comprende: ii.a) depositar una capa de nitruro de silicio sobre la superficie de silicio (2) ; ii.b) grabar la capa de nitruro de silicio hasta crear una máscara de nitruro de silicio sobre la superficie de silicio (2) ; ii.c) grabar la superficie de silicio (2) que no está protegida por la máscara de nitruro de silicio de manera que se forme el al menos un pilar de silicio (3) sobre la superficie de silicio (2) . 5. El método de acuerdo con la reivindicación 4, donde el grabado de la etapa (ii.b) es grabado isótropo o grabado anisótropo y/o donde el grabado de la etapa (ii.c) es grabado isótropo. 6. El método de acuerdo con una cualquiera de las reivindicaciones 3 a 5 donde el grabado de la etapa (iv) es grabado seco por plasma mediante la técnica ICP-RIE. 7. El método de acuerdo con una cualquiera de las reivindicaciones 3 a 6, donde la oxidación térmica de la etapa (iii) es oxidación húmeda u oxidación seca. 8. El método de acuerdo con la reivindicación 6, donde la oxidación de la etapa (iii) es oxidación húmeda y donde la oxidación húmeda se lleva a cabo en presencia de vapor a 1100°C durante al menos 12 horas. 9. El método de acuerdo con una cualquiera de las reivindicaciones 3 a 8, donde el pulido de la etapa (iii) y/o de la etapa (v) es pulido mecánico químico.

Los productos y servicios protegidos por este registro son:

H01L 21/02 - H01L 23/34 - H01L 31/024

Descripciones: