- Home /

- Publicaciones de patentes /

- MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL

Patente nacional por "MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL"

Este registro ha sido solicitado por

POWER ELECTRONICS ESPAÑA, S.L.

a través del representanteJAVIER UNGRÍA LÓPEZ

Contacto

- Estado: A punto de caducar

- País:

- España

- Fecha solicitud:

- 06/04/2022

- Número solicitud:

-

P202230307

- Número publicación:

-

ES2953912

- Fecha de concesión:

-

- Inventores:

-

Persona física

- Datos del titular:

-

POWER ELECTRONICS ESPAÑA, S.L.

- Datos del representante:

-

Javier Ungría López

- Clasificación Internacional de Patentes:

- H02M 3/335

- Clasificación Internacional de Patentes de la publicación:

- H02M 3/335

- Fecha de vencimiento:

Quiero registrar una patente

Reivindicaciones:

+ ES-2953912_A11- MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL, donde el convertidor DC/DC dual (10) comprende: • un bus interno del lado del campo solar fotovoltaico (12) que a su vez comprende: o un primer transistor (1B) , un segundo transistor (2B) , un tercer transistor (3B) , y un cuarto transistor (4B) conectados en serie; o resistencias (1R, 2R) y condensadores (1C, 2C) conectados en serie; donde los transistores (1B, 2B, 3B, 4B) conectados en serie están conectados en paralelo con las resistencias (1R, 1C) y los condensadores (1C, 2C) conectados en serie; y, donde bus interno del lado del campo solar fotovoltaico (12) es conectable con un campo solar fotovoltaico mediante unos segundos medios de cierre (27) ; • un bus interno del lado de baterías (20) que a su vez comprende: o un quinto transistor (5B) , un sexto transistor (6B) , un séptimo transistor (7B) y un octavo transistor (8B) conectados en serie; o resistencias (3R, 4R) y condensadores (1C, 2C) conectados en serie; donde los transistores conectados en serie (5B, 6B, 7B, 8B) están conectados en paralelo con las resistencias (3R, 4R) y los condensadores (1C, 2C) conectados en serie; y, donde bus interno del lado de baterías (20) es conectable con un rack de baterías mediante unos primeros medios de cierre (22, 25, 26) ; caracterizado porque el método comprende los siguientes pasos: i) conectar (30) el convertidor DC/DC dual (10) con el campo solar fotovoltaico (21) cerrando los segundos medios de cierre (27) y aislar el convertidor DC/DC (10) del rack de baterías (20) abriendo los primeros medios de cierre (22, 25, 26) ; ii) precargar (31) el bus interno del lado de baterías (12) al mismo voltaje respecto de tierra que tiene el rack de baterías (20) con energía procedente del campo solar fotovoltaico (21) mediante conmutaciones predefinidas de los transistores (1B, 2B, 3B, 4B, 5B, 6B, 7B, 8B) ; iii) aislar (32) el bus interno del lado de baterías (12) del bus interno del lado del campo solar fotovoltaico (11) hasta que el bus interno del lado de baterías (12) esté polarizado igual que el rack de baterías (20) , dejando abiertos los transistores (1B, 2B, 3B, 4B) del bus interno del lado del campo solar fotovoltaico (11) ; iv) conectar (33) el bus interno del lado de baterías (12) con el rack de baterías (20) , cerrando los primeros medios de cierre (22, 25, 26) ; v) abrir (34) el primer transistor (1B) , el cuarto transistor (4B) , el quinto transistor (5B) y el octavo transistor (8B) ; vi) polarizar (35) a un voltaje respecto de tierra el bus interno del lado de baterías (12) mediante conmutaciones sincronizadas del segundo transistor (2B) , del tercer transistor (3B) , del sexto transistor (6B) y del séptimo transistor (7B) donde las conmutaciones de los transistores se realizan en periodos de tiempo "T" con ciclos de trabajo crecientes n incrementos de tiempo desde un valor mínimo equivalente al tiempo de conmutación de los transistores hasta un valor máximo donde los transistores están cerrados. 2 - MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL, según la reivindicación 1, caracterizado porque el paso ii) adicionalmente comprende que el convertidor DC/DC dual funcione tipo "reductor" cuando el voltaje en el rack de baterías es inferior al voltaje en el campo solar fotovoltaico. 3 - MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL, según la reivindicación 1, caracterizado porque el paso ii) adicionalmente comprende que el convertidor DC/DC dual funcione tipo "elevador" cuando el voltaje en el rack de baterías es superior al voltaje en el campo solar fotovoltaico. 4 - MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL, según la reivindicación 2, caracterizado porque el paso ii) adicionalmente comprende: • abrir el sexto transistor (6B) y el séptimo transistor (7B) ; • cerrar el quinto transistor (5B) y el octavo transistor (8B) ; • conmutar el primer transistor (1B) , el segundo transistor (2B) , el tercer transistor (3B) , y el cuarto transistor (4B) . 5 - MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL, según la reivindicación 3, caracterizado porque el paso ii) adicionalmente comprende: • abrir el segundo transistor (2B) y el tercero transistor (3B) ; • cerrar el primero transistor (1B) y el cuarto transistor (4B) ; • conmutar el quinto transistor (5B) , el sexto transistor (6B) , el séptimo transistor (7B) y el octavo transistor (8B) . 6 - CONVERTIDOR DC/DC DUAL (10) , que comprende: • un bus interno del lado del campo solar fotovoltaico (12) que a su vez comprende: o un primer transistor (1B) , un segundo transistor (2B) , un tercer transistor (3B) , y un cuarto transistor (4B) conectados en serie; o resistencias (1R, 2R) y condensadores (1C, 2C) conectados en serie; donde los transistores (1B, 2B, 3B, 4B) conectados en serie están conectados en paralelo con las resistencias (1R, 1C) y los condensadores (1C, 2C) conectados en serie; y, donde bus interno del lado del campo solar fotovoltaico (12) es conectable con un campo solar fotovoltaico mediante unos segundos medios de cierre (27) ; • un bus interno del lado de baterías (20) que a su vez comprende: o un quinto transistor (5B) , un sexto transistor (6B) , un séptimo transistor (7B) y un octavo transistor (8B) conectados en serie; o resistencias (3R, 4R) y condensadores (1C, 2C) conectados en serie; donde los transistores conectados en serie (5B, 6B, 7B, 8B) están conectados en paralelo con las resistencias (3R, 4R) y los condensadores (1C, 2C) conectados en serie; y, donde bus interno del lado de baterías (20) es conectable con un rack de baterías mediante unos primeros medios de cierre (22, 25, 26) ; caracterizado porque comprende medios de control (28) conectados con al menos el primer transistor (1B) , el segundo transistor (2B) , el tercer transistor (3B) , el cuarto transistor (4B) , el quinto transistor (5B) , el sexto transistor (6B) , el séptimo transistor (7B) , el octavo transistor (8B) , los primeros medios de cierre (22, 25, 26) , los segundos medios de cierre (27) , donde los medios de control están configurados para llevar a cabo el método de polarización intrínseca de un convertidor DC/DC dual definido en una cualquiera de las reivindicaciones 1 a 5. 7.- CONVERTIDOR DC/DC DUAL (10) , según la reivindicación 6, donde los medios de control (28) están seleccionados entre un microcontrolador, un microprocesador y una FPGA.

Los productos y servicios protegidos por este registro son:

H02M 3/335

Descripciones:

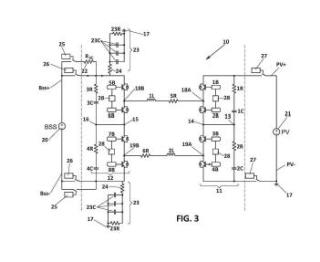

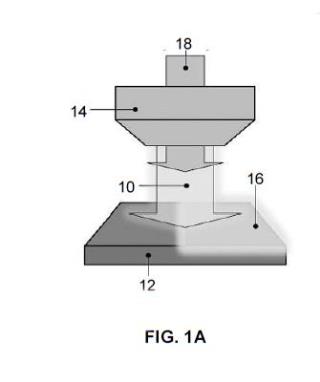

+ ES-2953912_A1 MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL CAMPO DE LA INVENCIÓN La presente invención se enmarca en la operativa en los convertidores DC/DC diferenciales sin aislamiento galvánico conectados a baterías y campo solar fotovoltaico como fuente de DC. El campo técnico de la invención se enmarca en el campo de la conversión de voltaje y especialmente en la conversión de altos voltajes con altas corrientes como sucede en los convertidores de potencia, controladores de motores y sistemas de generación de energía solar y eólica. ANTECEDENTES DE LA INVENCIÓN Los convertidores de potencia DC/DC duales, como el mostrado en la FIG. 1, son un tipo de convertidores DC/DC diferenciales que se utilizan habitualmente para cargar racks de baterías con la energía procedente de campos solares fotovoltaicos. En la industria de generación de energía renovable mediante campos solares fotovoltaicos existen dos configuraciones de puesta a tierra de los paneles fotovoltaicos: aislados de tierra (conocida como configuración de polos aislados) o conectar el polo negativo de los paneles fotovoltaicos a tierra (conocido como configuración de polo a tierra) . La configuración de polo a tierra presenta diferencias respecto a la configuración de polos aislados. Por citar alguna ventaja, la configuración polo a tierra evita la degradación inducida por potencial cuando no hay irradiancia (DIP, o más habitualmente PID por la expresión inglesa `Potential Induced Degradation') . El PID es una degradación que se produce en los paneles fotovoltaicos debido a la presencia de corrientes parásitas que produce una pérdida de rendimiento en los paneles. Su efecto potencial puede reducir la potencia del panel hasta en un 30%. A esta ventaja, se le suma que algunas normativas, como las de norte América o Japón obligan a las empresas generadoras de energía fotovoltaica a utilizar en sus plantas la configuración polo a tierra por razones de seguridad eléctrica. Esto entra en contraposición con los fabricantes de baterías, ya que la mayoría de los racks de baterías comerciales que existen en la actualidad recomiendan una configuración de polos aislados. Por tanto, los convertidores de potencia DC/DC diferenciales se utilizan para interconectar racks de baterías aislados de tierra con campos solares fotovoltaicos conectados a tierra. Para manejar grandes valores de potencia, se utilizan los convertidores DC/DC duales, los cuales tienen varios inconvenientes. Los más importantes inconvenientes son el transitorio de polarización al conectar las baterías al bus interno de condensadores del convertidor DC/DC dual y el transitorio de polarización al arrancar el convertidor DC/DC dual para su operación normal. Respecto del transitorio que se genera al arrancar el convertidor DC/DC dual para su operación normal, por tratarse de convertidores no aislados, en parado existe una diferencia de potenciales que se igualan forzosamente cuando el convertidor DC/DC dual comienza a funcionar. Se provoca, por tanto, en el lado del convertidor DC/DC dual que no está conectado a tierra (lado de baterías) un transitorio de tensión y corriente hasta igualar los voltajes del campo solar fotovoltaico y de las baterías. Si por ejemplo, el campo solar fotovoltaico tiene un voltaje positivo de 1000 voltios y un voltaje negativo de 0 voltios porque está conectado a tierra, y las baterías tienen un voltaje positivo de 500 voltios y un voltaje negativo de -500 voltios, ambos respecto a tierra, porque están aisladas, al empezar a funcionar el convertidor DC/DC, se producirá un transitorio en el interior del mismo hasta que las baterías se encuentren polarizadas igual que el campo solar fotovoltaico. Es decir, se producirá un transitorio hasta que las baterías se encuentren a un voltaje positivo de 1000 voltios y un voltaje negativo de 0 voltios respecto de tierra. La solución del estado de la técnica respecto del transitorio que se genera al arrancar el convertidor DC/DC dual para su operación normal es dimensionar los componentes del mismo (resistencias, condensadores, transistores mostrados en la Fig. 1) para que sean capaces de soportar los picos de voltaje y corriente que se generan durante el transitorio. Respecto del transitorio que se genera al conectar el rack de baterías al bus de condensadores interno del convertidor DC/DC dual, se conoce en el estado de la técnica la conexión mediante una resistencia que se conoce como "carga suave resistiva-pasiva". La solicitud del estado de la técnica consiste en una resistencia "RSc" (ver Fig. 3) conectada entre el lado interno del convertidor DC/DC y las baterías. El problema que ocurre con la solución del estado de la técnica es que se produce un transitorio al cierre de contactores de carga suave, puesto que el bus interno del lado de baterías (Fig. 3 - 12) no se encontrará al mismo potencial que las baterías (Fig. 3 - 20) . Por ejemplo, si el el bus interno del lado de baterías parte descargado "0 voltios" es imposible que ambos potenciales "BSS+" y "BSS-"coincidan (ver Fig. 3) . Adicionalmente, se produce un pico de corriente extra que puede afectar a la carga suave. En la Fig. 2 pueden observarse el voltaje BSS+ (tensión diferencial en el lado interno de baterías) y el voltaje BSS- (potencial respecto a tierra del negativo del lado interno de baterías) . Por todo lo anterior, surge la necesidad de crear una solución que permita tener un convertidor DC/DC dual capaz de trabajar en el lado de paneles fotovoltaicos con polo a tierra y en el lado de baterías trabajar con polos aislados evitando este tipo de transitorios, lo cual permitiría dimensionar el convertidor DC/DC dual a los voltajes y corrientes normales de funcionamiento reduciendo peso de los convertidores y costes de fabricación de los mismos. OBJETO DE LA INVENCIÓN La presente invención proporciona una solución al problema anterior mediante un método que pre-carga y polarización del convertidor DC/DC dual para que al empezar a funcionar el convertidor DC/DC dual de forma normal, las baterías "BSS" y el campo solar fotovoltaico "PV" se encuentren al mismo voltaje respecto de tierra. La solución aportada permite a un convertidor DC/DC dual no aislado operar de forma segura y sin producir daños en una configuración de campo solar fotovoltaico "PV" con polos a tierra y baterías "BSS" flotante (polos aislados) . Es decir, la solución aportada elimina ambos transitorios por polarización que se producen en los convertidores DC/DC duales del estado de la técnica. DESCRIPCIÓN DE LA INVENCIÓN La presente invención divulga un método de polarización intrínseca de un convertidor DC/DC dual que es capaz de eliminar el transitorio de polarización al conectar el rack de baterías al bus interno del convertidor DC/DC dual y el transitorio de polarización al arrancar el convertidor DC/DC dual para su operación normal. La topología del convertidor DC/DC dual comprende, al menos, un bus interno del lado del campo solar fotovoltaico y un bus interno del lado de baterías. El bus interno del lado del campo solar fotovoltaico a su vez comprende: un primer transistor, un segundo transistor, un tercer transistor, y un cuarto transistor, conectados en serie. Adicionalmente, el bus interno del lado del campo solar fotovoltaico comprende unas resistencias y unos condensadores conectados en serie. Los transistores conectados en serie están conectados en paralelo con las resistencias y los condensadores conectados en serie. Además, el bus interno del lado del campo solar fotovoltaico es conectable con un campo solar fotovoltaico mediante unos segundos medios de cierre. Por su parte, el bus interno del lado de baterías a su vez comprende: un quinto transistor, un sexto transistor, un séptimo transistor y un octavo transistor conectados en serie. Adicionalmente, el bus interno del lado de baterías comprende unas resistencias y condensadores conectados en serie. Los transistores conectados en serie están conectados en paralelo con las resistencias y los condensadores conectados en serie. El bus interno del lado de baterías es conectable con un rack de baterías mediante unos primeros medios de cierre. Los primeros y segundos medios de cierre pueden ser contactores. Adicionalmente, los primeros medios de cierre pueden comprender una resistencia "RSC" en serie con el contactor para realizar la carga suave pasiva conocida en el estado de la técnica. El convertidor DC/DC dual puede comprender filtros RFI que filtran las frecuencias altas. Los filtros RFI conectan el bus interno del lado de baterías con tierra. Los filtros RFI pueden comprender varios condensadores y una resistencia en paralelo, y una resistencia en serie para unir el filtro con el bus interno del lado de baterías. El convertidor DC/DC dual puede comprender unos medios de control conectados con al menos: el primer transistor, el segundo transistor, el tercer transistor, el cuarto transistor, el quinto transistor, el sexto transistor, el séptimo transistor, el octavo transistor, los primeros medios de cierre, los segundos medios de cierre, donde los medios de control están configurados para llevar a cabo el método de polarización intrínseca de la presente invención que se detalla a continuación. Los medios de control pueden estar seleccionados entre un microcontrolador, un microprocesador y una FPGA. Para la topología del convertidor DC/DC dual descrito previamente, el método de polarización intrínseca de la presente invención comprende los siguientes pasos: i) conectar el convertidor DC/DC dual con el campo solar fotovoltaico cerrando los segundos medios de cierre y aislar el convertidor DC/DC del rack de baterías abriendo los primeros medios de cierre; ii) precargar el bus interno del lado de baterías al mismo voltaje respecto de tierra que tiene el rack de baterías con energía procedente del campo solar fotovoltaico mediante conmutaciones predefinidas de (todos) los transistores; iii) aislar el bus interno del lado de baterías del bus interno del lado del campo solar fotovoltaico hasta que el bus interno del lado de baterías esté polarizado igual que el rack de baterías (=pasar el bus interno del lado de baterías de modo diferencial con negativo a tierra a modo diferencial donde los lados positivos y negativos están equidistantes de tierra) , dejando abiertos los transistores del bus interno del lado del campo solar fotovoltaico; iv) conectar el bus interno del lado de baterías con el rack de baterías, cerrando los primeros medios de cierre; v) abrir el primer transistor, el cuarto transistor, el quinto transistor y el octavo transistor; i) polarizar a un voltaje respecto de tierra el bus interno del lado de baterías (y por tanto, también el rack de baterías porque están conectados) mediante conmutaciones sincronizadas del segundo transistor, del tercer transistor, del sexto transistor y del séptimo transistor donde las conmutaciones de los transistores se realizan en periodos de tiempo "T" con ciclos de trabajo crecientes en incrementos de tiempo desde un valor mínimo equivalente al tiempo de conmutación de los transistores hasta un valor máximo donde los transistores están cerrados, para que no haya transferencia de energía entre los lados internos del convertidor ya que la poca energía generada en las conmutaciones se disipará en las resistencias y bobinas que unen ambos lados internos. En una forma de realización, el paso ii) adicionalmente comprende que el convertidor DC/DC dual funcione tipo "reductor" (Buck) cuando el voltaje en el rack de baterías es inferior al voltaje en el campo solar fotovoltaico. Por tanto, las conmutaciones predefinidas del paso ii) del método de la presente invención, para que el convertidor DC/DC dual funcione tipo "reductor" (Buck) comprenden al menos: • abrir el sexto transistor y el séptimo transistor; • cerrar el quinto transistor y el octavo transistor; y, • conmutar el primer transistor, el segundo transistor, el tercer transistor, y el cuarto transistor. En una forma de realización, el paso ii) adicionalmente comprende que el convertidor DC/DC dual funcione tipo "elevador" (Boost) cuando el voltaje en el rack de baterías es superior al voltaje en el campo solar fotovoltaico. Por tanto, las conmutaciones predefinidas del paso ii) del método de la presente invención, para que el convertidor DC/DC dual funcione tipo "elevador" (Boost) comprenden al menos: • abrir el segundo transistor y el tercero transistor; • cerrar el primero transistor y el cuarto transistor; y, • conmutar el quinto transistor, el sexto transistor, el séptimo transistor y el octavo transistor. En toda la presente memoria descriptiva, se entenderá de forma equivalente los términos "batería", "baterías" y "rack de baterías". BREVE DESCRIPCIÓN DE LAS FIGURAS. Fig. 1.- Se muestra un convertidor DC/DC diferencial de tipo "dual" conectado a un campo solar fotovoltaico y a un rack de baterías. Fig.2.- Se muestra los transitorios que sufren los polos positivo y negativo del rack de baterías cuando se conecta el convertidor DC/DC dual del estado de la técnica al rack de baterías. Fig. 3.- Se muestra un convertidor DC/DC diferencial de tipo "dual" conectado a un campo solar fotovoltaico y a un rack de baterías, donde el convertidor DC/DC dual tiene una resistencia de carga suave pasiva y filtros RFI. Fig. 4.- Se muestra un diagrama de flujo del método de la presente invención. Fig. 5.- Se muestran los componentes que se activan para llevar a cabo la polarización del rack de baterías. REALIZACIÓN PREFERENTE DE LA INVENCIÓN. En la Fig. 1 se muestra un convertidor DC/DC diferencial de tipo "dual" 10 conectado a un campo solar fotovoltaico "PV" 21 y a un rack de baterías "BSS" 20. El convertidor DC/DC dual 10 tiene el bus interno del lado del campo solar fotovoltaico 11 y el bus interno del lado de baterías 12. El bus interno del lado del campo solar fotovoltaico 11 tiene el primer transistor 1B, el segundo transistor 2B, el tercer transistor 3B y el cuarto transistor 4B conectados en serie. Adicionalmente, el bus interno del lado del campo solar fotovoltaico 11 tiene la primera resistencia 1R, el primer condensador 1C, la segunda resistencia 2R y el segundo condensador 2C conectados en serie, los cuales a su vez están conectados en paralelo con los cuatro transistores 1B-4B, tal y como se muestra en la Fig. 1. En la Fig. 1 también se observa que el punto medio 14 de la rama de los cuatro transistores 1B-4B está conectado con el punto medio 13 de la rama de los condensadores y resistencias 1R-1C-2R-2C. El bus interno del lado del campo solar fotovoltaico 11 está conectado a tierra 17, lo que da lugar a la "configuración de polo a tierra" del lado del campo solar fotovoltaico 21. El bus interno del lado de baterías 12 tiene el quinto transistor 5B, el sexto transistor 6B, el séptimo transistor 7B y el octavo transistor 8B conectados en serie. Adicionalmente, el bus interno del lado de baterías 12 tiene la tercera resistencia 3R, el tercer condensador 3C, la cuarta resistencia 4R y el cuarto condensador 4C conectados en serie, los cuales a su vez están conectados en paralelo con los cuatro transistores 5B, 6B, 7B, 8B, tal y como se muestra en la Fig. 1. En la Fig. 1 también se observa que el punto medio 15 de la rama de los cuatro transistores 5B-8B está conectado con el punto medio 16 de la rama de los condensadores y resistencias 3R-3C-4R-4C. El bus interno del lado de baterías 12 no está conectado a tierra, lo que da lugar a la "configuración de polos aislados" del lado de baterías 20. Finalmente, en la Fig. 1, se puede observar que el bus interno del lado del campo solar fotovoltaico 11 y el bus interno del lado de baterías 12 están conectados entre sí por bobinas y esistencias. Concretamente, el punto de conexión 18A entre el primer transistor 1B y el segundo transistor 2B está conectado con el punto de conexión 18B entre el quinto transistor 5B y el sexto transistor 6B, mediante la primera bobina 1L y la quinta resistencia 5R. Adicionalmente, el punto de conexión 19A entre el tercer transistor 3B y el cuarto transistor 4B está conectado con el punto de conexión 19B entre el séptimo transistor 7B y el octavo transistor 8B, mediante la segunda bobina 2L y la sexta resistencia 6R. En la Fig. 2 se muestran los transitorios de polarización que sufren los polos positivo y negativo del rack de baterías cuando se conecta el convertidor DC/DC dual del estado de la técnica al rack de baterías y que no se producen al aplicar el método de la presente invención. En la Fig. 3 se muestra el convertidor DC/DC diferencial de tipo "dual" 10 de la Fig. 1 conectado al campo solar fotovoltaico 21 mediantes los contactores 27. Adicionalmente, el convertidor DC/DC dual 10 se conecta con el rack de baterías 20 mediante una configuración de carga suave formada la resistencia "RSC" 22 y los contactores 25. Y una vez terminada la carga suave, se conecta el rack de baterías 20 con el convertidor DC/DC dual mediante los contactores 26 como es conocido en el estado de la técnica. Siguiendo con la Fig. 3, también es conocido en el estado de la técnica que el bus interno del lado de baterías 12 del convertidor DC/DC dual, si bien no está conectado a tierra directamente en la configuración de "polos aislados", dicho bus interno del lado de baterías 12 sí está conectado a tierra mediante los filtros "RFI" 23 encargados de filtrar las altas frecuencias. En el caso mostrado en la Fig.3, los filtros RFI están formados por tres condensadores 23C y una resistencia 23R conectados en paralelo y por una resistencia 24 que conecta cada rama del bus interno del lado del lado de baterías 12 con tierra. Para la configuración de un convertidor DC/DC diferencial de tipo "dual" 10 como el mostrado en las figuras 1 y 3, la presente invención divulga un método de polarización intrínseca del convertidor DC/DC dual que, mediante una precarga y una polarización interna, es capaz de eliminar el transitorio de polarización al conectar las baterías al bus interno del convertidor DC/DC dual y el transitorio de polarización al arrancar el convertidor DC/DC dual para su operación normal. Por tanto, el método de la presente invención comprende realizar una precarga activa del convertidor DC/DC dual. Pero antes, el convertidor DC/DC dual 10 tiene que estar conectado al campo solar fotovoltaico "PV" 21 y desconectado del rack de baterías "BSS" 20. Es decir, los contactores 27 están cerrados y los contactores 25 y 26 de la figura 3 están abiertos. Por tanto, el primer paso del método es conectar (Fig. 4 - 30) el convertidor DC/DC dual 10 con el campo solar fotovoltaico 21 cerrando el contactor 27 y mantener aislado el convertidor DC/DC 10 del rack de baterías 20 manteniendo abiertos los contactores 25 y 26. A continuación (Fig. 4 - 31) , e lleva a cabo la precarga activa que comprende igualar de forma controlada y progresiva el voltaje interno (el voltaje de los buses internos de baterías 12 y PV 11) respecto de tierra del DC/DC dual 10 al valor de voltaje que tiene el rack de baterías 20 en modo diferencial equidistante de tierra. Por ejemplo, si el rack de baterías 20 tiene un voltaje en modo diferencial de 1000v (-500v y +500v respecto a GND) y el campo solar fotovoltaico PV 21 tiene un voltaje de 1200v en modo diferencial (entre 0v y 1200v respeto a GND) respecto a tierra, los buses internos 11 y 12 del convertidor DC/DC dual 10 se precargan a 1000v en modo diferencial (entre 0v y 1000v respecto a GND) respecto a tierra con energía procedente del campo solar fotovoltaico PV 21. Nótese que el convertidor DC/DC dual 10 es no aislado y la polarización del campo solar fotovoltaico PV coincide con la de los buses internos cuando los transistores del convertidor DC/DC conmutan. Para llevar a cabo la transferencia de potencia (energía) desde el campo solar fotovoltaico PV 21 hasta el bus interno de baterías 12, para la transferencia final al rack de baterías 20, hay que conocer el voltaje en el campo solar fotovoltaico PV 21 y el voltaje en el rack de baterías 20. Si el voltaje en el rack de baterías 20 es menor que el voltaje en el campo solar fotovoltaico PV 21 (VBSs < VPV) , el convertidor DC/DC dual 10 funcionará como un reductor 31A ("Buck") donde se abrirán el sexto transistor 6B y el séptimo transistor 7B, cerrarán el quinto transistor 5B y el octavo transistor 8B, y conmutarán todos los transistores (el primer transistor 1B, el segundo transistor 2B, el tercer transistor 3B, y el cuarto transistor 4B) del lado del campo solar fotovoltaico PV, generando en bornas de la inductancia 1L una tensión superior a la del lado de baterías a cargar para provocar el flujo de potencia. Mientras que, si el voltaje en el rack de baterías 20 es mayor que el voltaje en el campo solar fotovoltaico PV 21 (VBSS > VPV) , el convertidor DC/DC dual 10 funcionará como un elevador 31B ("Boost") . El tipo de conmutación de los transistores para el caso "elevador" será la contraria a la explicada para el caso "reductor", donde se abrirán el segundo transistor 2B y el tercero transistor 3B, cerrarán el primero transistor 1B y el cuarto transistor 4B, y conmutarán todos los transistores del lado de baterías (el quinto transistor 5B, el sexto transistor 6B, el séptimo transistor 7B y el octavo transistor 8B) . Una vez que mediante la precarga activa se consigue que el voltaje interno (el voltaje de los buses internos de baterías 12 y PV 11) del DC/DC dual 10 en modo diferencial respecto de tierra sea igual al valor de voltaje que tiene el rack de baterías 20 en modo diferencial (equidistante de tierra) , el siguiente paso del método es aislar (Fig. 4, 32) el bus interno del lado de baterías 12 del bus interno del lado del campo solar fotovoltaico PV 11 hasta que el bus interno del lado de baterías 12 esté polarizado igual que el rack de baterías 20. Es decir, aislar el bus interno del lado de baterías 12 para que de forma natural, el bus interno del lado de baterías 12 tenga el mismo voltaje tanto en modo diferencial como respecto a tierra ("GND") . Para aislar el bus interno del lado de baterías 12, el método comprende dejar abiertos los ransistores 1B, 2B, 3B y 4B del bus interno del lado del campo solar fotovoltaico 11. Siguiendo con el ejemplo anterior, el bus interno del lado de baterías 12 tendría un voltaje de 1000v en modo diferencial respecto a tierra (1000.- 0v) antes de aislar el propio bus interno del lado de baterías 12. Al aislar el bus interno del lado de baterías 12, el bus interno del lado de baterías 12 de forma natural mantiene el voltaje de 1000v en modo diferencial pero modifica su voltaje en modo común o respecto a tierra (-500v sobre GND y +500v sobre GND) . Teniendo en cuenta que el voltaje en modo diferencial "VDIFF" se define como VDIFF = V2 - Vi; y voltaje en modo común "VMC" de define como VMC = (V2 + V1) /2, el VDIFF se mantiene en 1000v, pero el voltaje en modo común "VMC" pasa de 500v (= (1000-0) /2) a 0v (= (+500+ (-500) ) /2) . A continuación, el método comprende conectar (Fig. 4, 33) el bus interno del lado de baterías 12 con el rack de baterías 20. Como el bus interno del lado de baterías 12 tiene el mismo voltaje y misma polarización que el rack de baterías 12, no se produce el transitorio de polarización que se producía en el estado de la técnica al conectar las baterías al bus interno de condensadores del convertidor DC/DC dual. Para conectar el convertidor DC/DC dual 10 de la figura 3 con el rack de baterías 12, se realiza la "carga suave" mediante el cierre de los contactores 25 y la resistencia 22 según se conoce en estado de la técnica. Posteriormente, se cierra el contactor 26. Llegados a este punto, el bus interno del lado de baterías 12 estará polarizado en modo diferencial equidistante de tierra y el bus interno del lado del campo solar fotovoltaico 11 estará polarizado en modo diferencial respecto de tierra. Siguiendo con el ejemplo anterior, el bus interno del lado de baterías 12 tendría un voltaje diferencial de 1000v, polo negativo a -500v y polo positivo a +500v, y el bus interno del lado del campo solar fotovoltaico 11 tendría un voltaje diferencial de 1000v, polo positivo a +1000v y polo negativo a 0v. Esto provocaría un transitorio al comenzar el convertidor 10 a funcionar de modo normal. Todo lo anterior se puede ejemplificar con la siguiente tabla: Tabla 1 Para evitar el transitorio de "puesta en marcha", la presente invención propone polarizar el rack de baterías 20 con el objetivo de igualar los voltajes respecto a tierra "GND" antes de entrar en operación ("ON") . La polarización consiste principalmente en conmutar los transistores de potencia en una posición que no genere traspaso de energía. Para ello, se conmutan unos transistores concretos con un ciclo de trabajo lo más pequeño posible y progresivo, pero que iguale de un modo progresivo los potenciales en ambos lados internos (11, 12) del convertidor DC/DC dual. Antes de iniciar la polarización del rack de baterías 20, es necesario abrir (Fig. 4 - 34) los transistores externos (1B, 4B, 5B, 8B) del convertidor DC/DC dual. Una vez abiertos los transistores externos (1B, 4B, 5B, 8B) , ya es posible conmutar (Fig. 4 - 35) los transistores intermedios (2B, 3B, 6B, 7B) con el menor ciclo de trabajo posible hasta que el ciclo de trabajo sea igual a "1" (Fig. 4 - 37) con incrementos de tiempo At (Fig. 4 - 36) . El ciclo de trabajo mínimo será el que permita el propio transistor en función de la tecnología con la que esté fabricado el transistor de potencia. A modo de ejemplo un tiempo entre 1-3^s puede tomarse como referencia con el empleo de transistores de tipo IGBTs. El ciclo de trabajo se incrementa de modo progresivo hasta dejar los transistores 2B, 3B, 6B, 7B cerrados, momento en el cual la polarización está completada. Esto hace que comiencen a igualarse progresivamente los voltajes de ambos lados internos (11, 12) del convertidor DC/DC dual 10 de un modo que aparte de ser muy bajo en cuanto a energía (debido a que el ciclo es el mínimo posible y se incrementa lentamente) , se ve atenuado por el filtro paso-bajo implícito de las inductancias que hay entre ambos lados internos (11, 12) del convertidor DC/DC dual 10 (camino marcado con línea discontinua en la Fig. 5 donde se dibujan unas capacidades parásitas "C" de los buses) . Los incrementos de tiempo At en el ciclo de trabajo "CT" dependerán principalmente del filtro paso-bajo implícito de las inductancias y de la tecnología de los transistores (1B-8B) de potencia y sólo deben cumplirse la condición de que no haya traspaso de energía entre ambos lados internos (11, 12) del convertidor DC/DC dual 10. A modo de ejemplo, un tiempo entre 1-3^s puede tomarse como referencia para los incrementos de tiempo At con el empleo de transistores de tipo IGBTs. A continuación se incluye una comparativa entre el funcionamiento del convertidor DC/DC dual según el estado de la técnica y el funcionamiento del mismo para la polarización del lado interno de baterías 12, y por tanto, del rack de baterías 20 cuando están ambos conectados: Tabla 2 Para llevar a cabo el método de polarización intrínseca de un convertidor DC/DC dual de la presente invención, el convertidor DC/DC dual comprende unos medios de control 28 conectados con al menos: el primer transistor, el segundo transistor, el tercer transistor, el cuarto transistor, el quinto transistor, el sexto transistor, el séptimo transistor, el octavo transistor, los primeros medios de cierre, los segundos medios de cierre. Los medios de control pueden estar seleccionados entre un microcontrolador, un microprocesador y una FPGA.

Publicaciones:

ES2953912 (17/11/2023) - A1 Solicitud de patente con informe sobre el estado de la técnica

Eventos:

En fecha 06/04/2022 se realizó Registro Instancia de Solicitud

En fecha 07/04/2022 se realizó Admisión a Trámite

En fecha 07/04/2022 se realizó 1001P_Comunicación Admisión a Trámite

En fecha 08/04/2022 se realizó Superado examen de oficio

En fecha 07/11/2022 se realizó Realizado IET

En fecha 14/11/2022 se realizó 1109P_Comunicación Traslado del IET

En fecha 17/11/2023 se realizó Publicación Solicitud

En fecha 17/11/2023 se realizó Publicación Folleto Solicitud con IET (A1)

En fecha 15/02/2024 se realizó PETEX_Petición de examen sustantivo

En fecha 04/03/2024 se realizó Validación petición y/o pago de examen sustantivo conforme

En fecha 07/03/2024 se realizó El solicitante ha contestado pero existen nuevas objeciones a la concesión de la solicitud

En fecha 07/03/2024 se realizó Elaboración de examen sustantivo

En fecha 07/03/2024 se realizó 6120P_Notificación de examen sustantivo

En fecha 13/03/2024 se realizó Publicación de examen sustantivo

Pagos:

05/04/2022 - Pago Tasas IET

+ ES-2953912_A11- MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL, donde el convertidor DC/DC dual (10) comprende: • un bus interno del lado del campo solar fotovoltaico (12) que a su vez comprende: o un primer transistor (1B) , un segundo transistor (2B) , un tercer transistor (3B) , y un cuarto transistor (4B) conectados en serie; o resistencias (1R, 2R) y condensadores (1C, 2C) conectados en serie; donde los transistores (1B, 2B, 3B, 4B) conectados en serie están conectados en paralelo con las resistencias (1R, 1C) y los condensadores (1C, 2C) conectados en serie; y, donde bus interno del lado del campo solar fotovoltaico (12) es conectable con un campo solar fotovoltaico mediante unos segundos medios de cierre (27) ; • un bus interno del lado de baterías (20) que a su vez comprende: o un quinto transistor (5B) , un sexto transistor (6B) , un séptimo transistor (7B) y un octavo transistor (8B) conectados en serie; o resistencias (3R, 4R) y condensadores (1C, 2C) conectados en serie; donde los transistores conectados en serie (5B, 6B, 7B, 8B) están conectados en paralelo con las resistencias (3R, 4R) y los condensadores (1C, 2C) conectados en serie; y, donde bus interno del lado de baterías (20) es conectable con un rack de baterías mediante unos primeros medios de cierre (22, 25, 26) ; caracterizado porque el método comprende los siguientes pasos: i) conectar (30) el convertidor DC/DC dual (10) con el campo solar fotovoltaico (21) cerrando los segundos medios de cierre (27) y aislar el convertidor DC/DC (10) del rack de baterías (20) abriendo los primeros medios de cierre (22, 25, 26) ; ii) precargar (31) el bus interno del lado de baterías (12) al mismo voltaje respecto de tierra que tiene el rack de baterías (20) con energía procedente del campo solar fotovoltaico (21) mediante conmutaciones predefinidas de los transistores (1B, 2B, 3B, 4B, 5B, 6B, 7B, 8B) ; iii) aislar (32) el bus interno del lado de baterías (12) del bus interno del lado del campo solar fotovoltaico (11) hasta que el bus interno del lado de baterías (12) esté polarizado igual que el rack de baterías (20) , dejando abiertos los transistores (1B, 2B, 3B, 4B) del bus interno del lado del campo solar fotovoltaico (11) ; iv) conectar (33) el bus interno del lado de baterías (12) con el rack de baterías (20) , cerrando los primeros medios de cierre (22, 25, 26) ; v) abrir (34) el primer transistor (1B) , el cuarto transistor (4B) , el quinto transistor (5B) y el octavo transistor (8B) ; vi) polarizar (35) a un voltaje respecto de tierra el bus interno del lado de baterías (12) mediante conmutaciones sincronizadas del segundo transistor (2B) , del tercer transistor (3B) , del sexto transistor (6B) y del séptimo transistor (7B) donde las conmutaciones de los transistores se realizan en periodos de tiempo "T" con ciclos de trabajo crecientes n incrementos de tiempo desde un valor mínimo equivalente al tiempo de conmutación de los transistores hasta un valor máximo donde los transistores están cerrados. 2 - MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL, según la reivindicación 1, caracterizado porque el paso ii) adicionalmente comprende que el convertidor DC/DC dual funcione tipo "reductor" cuando el voltaje en el rack de baterías es inferior al voltaje en el campo solar fotovoltaico. 3 - MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL, según la reivindicación 1, caracterizado porque el paso ii) adicionalmente comprende que el convertidor DC/DC dual funcione tipo "elevador" cuando el voltaje en el rack de baterías es superior al voltaje en el campo solar fotovoltaico. 4 - MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL, según la reivindicación 2, caracterizado porque el paso ii) adicionalmente comprende: • abrir el sexto transistor (6B) y el séptimo transistor (7B) ; • cerrar el quinto transistor (5B) y el octavo transistor (8B) ; • conmutar el primer transistor (1B) , el segundo transistor (2B) , el tercer transistor (3B) , y el cuarto transistor (4B) . 5 - MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL, según la reivindicación 3, caracterizado porque el paso ii) adicionalmente comprende: • abrir el segundo transistor (2B) y el tercero transistor (3B) ; • cerrar el primero transistor (1B) y el cuarto transistor (4B) ; • conmutar el quinto transistor (5B) , el sexto transistor (6B) , el séptimo transistor (7B) y el octavo transistor (8B) . 6 - CONVERTIDOR DC/DC DUAL (10) , que comprende: • un bus interno del lado del campo solar fotovoltaico (12) que a su vez comprende: o un primer transistor (1B) , un segundo transistor (2B) , un tercer transistor (3B) , y un cuarto transistor (4B) conectados en serie; o resistencias (1R, 2R) y condensadores (1C, 2C) conectados en serie; donde los transistores (1B, 2B, 3B, 4B) conectados en serie están conectados en paralelo con las resistencias (1R, 1C) y los condensadores (1C, 2C) conectados en serie; y, donde bus interno del lado del campo solar fotovoltaico (12) es conectable con un campo solar fotovoltaico mediante unos segundos medios de cierre (27) ; • un bus interno del lado de baterías (20) que a su vez comprende: o un quinto transistor (5B) , un sexto transistor (6B) , un séptimo transistor (7B) y un octavo transistor (8B) conectados en serie; o resistencias (3R, 4R) y condensadores (1C, 2C) conectados en serie; donde los transistores conectados en serie (5B, 6B, 7B, 8B) están conectados en paralelo con las resistencias (3R, 4R) y los condensadores (1C, 2C) conectados en serie; y, donde bus interno del lado de baterías (20) es conectable con un rack de baterías mediante unos primeros medios de cierre (22, 25, 26) ; caracterizado porque comprende medios de control (28) conectados con al menos el primer transistor (1B) , el segundo transistor (2B) , el tercer transistor (3B) , el cuarto transistor (4B) , el quinto transistor (5B) , el sexto transistor (6B) , el séptimo transistor (7B) , el octavo transistor (8B) , los primeros medios de cierre (22, 25, 26) , los segundos medios de cierre (27) , donde los medios de control están configurados para llevar a cabo el método de polarización intrínseca de un convertidor DC/DC dual definido en una cualquiera de las reivindicaciones 1 a 5. 7.- CONVERTIDOR DC/DC DUAL (10) , según la reivindicación 6, donde los medios de control (28) están seleccionados entre un microcontrolador, un microprocesador y una FPGA.

Los productos y servicios protegidos por este registro son:

H02M 3/335

Descripciones:

+ ES-2953912_A1 MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL CAMPO DE LA INVENCIÓN La presente invención se enmarca en la operativa en los convertidores DC/DC diferenciales sin aislamiento galvánico conectados a baterías y campo solar fotovoltaico como fuente de DC. El campo técnico de la invención se enmarca en el campo de la conversión de voltaje y especialmente en la conversión de altos voltajes con altas corrientes como sucede en los convertidores de potencia, controladores de motores y sistemas de generación de energía solar y eólica. ANTECEDENTES DE LA INVENCIÓN Los convertidores de potencia DC/DC duales, como el mostrado en la FIG. 1, son un tipo de convertidores DC/DC diferenciales que se utilizan habitualmente para cargar racks de baterías con la energía procedente de campos solares fotovoltaicos. En la industria de generación de energía renovable mediante campos solares fotovoltaicos existen dos configuraciones de puesta a tierra de los paneles fotovoltaicos: aislados de tierra (conocida como configuración de polos aislados) o conectar el polo negativo de los paneles fotovoltaicos a tierra (conocido como configuración de polo a tierra) . La configuración de polo a tierra presenta diferencias respecto a la configuración de polos aislados. Por citar alguna ventaja, la configuración polo a tierra evita la degradación inducida por potencial cuando no hay irradiancia (DIP, o más habitualmente PID por la expresión inglesa `Potential Induced Degradation') . El PID es una degradación que se produce en los paneles fotovoltaicos debido a la presencia de corrientes parásitas que produce una pérdida de rendimiento en los paneles. Su efecto potencial puede reducir la potencia del panel hasta en un 30%. A esta ventaja, se le suma que algunas normativas, como las de norte América o Japón obligan a las empresas generadoras de energía fotovoltaica a utilizar en sus plantas la configuración polo a tierra por razones de seguridad eléctrica. Esto entra en contraposición con los fabricantes de baterías, ya que la mayoría de los racks de baterías comerciales que existen en la actualidad recomiendan una configuración de polos aislados. Por tanto, los convertidores de potencia DC/DC diferenciales se utilizan para interconectar racks de baterías aislados de tierra con campos solares fotovoltaicos conectados a tierra. Para manejar grandes valores de potencia, se utilizan los convertidores DC/DC duales, los cuales tienen varios inconvenientes. Los más importantes inconvenientes son el transitorio de polarización al conectar las baterías al bus interno de condensadores del convertidor DC/DC dual y el transitorio de polarización al arrancar el convertidor DC/DC dual para su operación normal. Respecto del transitorio que se genera al arrancar el convertidor DC/DC dual para su operación normal, por tratarse de convertidores no aislados, en parado existe una diferencia de potenciales que se igualan forzosamente cuando el convertidor DC/DC dual comienza a funcionar. Se provoca, por tanto, en el lado del convertidor DC/DC dual que no está conectado a tierra (lado de baterías) un transitorio de tensión y corriente hasta igualar los voltajes del campo solar fotovoltaico y de las baterías. Si por ejemplo, el campo solar fotovoltaico tiene un voltaje positivo de 1000 voltios y un voltaje negativo de 0 voltios porque está conectado a tierra, y las baterías tienen un voltaje positivo de 500 voltios y un voltaje negativo de -500 voltios, ambos respecto a tierra, porque están aisladas, al empezar a funcionar el convertidor DC/DC, se producirá un transitorio en el interior del mismo hasta que las baterías se encuentren polarizadas igual que el campo solar fotovoltaico. Es decir, se producirá un transitorio hasta que las baterías se encuentren a un voltaje positivo de 1000 voltios y un voltaje negativo de 0 voltios respecto de tierra. La solución del estado de la técnica respecto del transitorio que se genera al arrancar el convertidor DC/DC dual para su operación normal es dimensionar los componentes del mismo (resistencias, condensadores, transistores mostrados en la Fig. 1) para que sean capaces de soportar los picos de voltaje y corriente que se generan durante el transitorio. Respecto del transitorio que se genera al conectar el rack de baterías al bus de condensadores interno del convertidor DC/DC dual, se conoce en el estado de la técnica la conexión mediante una resistencia que se conoce como "carga suave resistiva-pasiva". La solicitud del estado de la técnica consiste en una resistencia "RSc" (ver Fig. 3) conectada entre el lado interno del convertidor DC/DC y las baterías. El problema que ocurre con la solución del estado de la técnica es que se produce un transitorio al cierre de contactores de carga suave, puesto que el bus interno del lado de baterías (Fig. 3 - 12) no se encontrará al mismo potencial que las baterías (Fig. 3 - 20) . Por ejemplo, si el el bus interno del lado de baterías parte descargado "0 voltios" es imposible que ambos potenciales "BSS+" y "BSS-"coincidan (ver Fig. 3) . Adicionalmente, se produce un pico de corriente extra que puede afectar a la carga suave. En la Fig. 2 pueden observarse el voltaje BSS+ (tensión diferencial en el lado interno de baterías) y el voltaje BSS- (potencial respecto a tierra del negativo del lado interno de baterías) . Por todo lo anterior, surge la necesidad de crear una solución que permita tener un convertidor DC/DC dual capaz de trabajar en el lado de paneles fotovoltaicos con polo a tierra y en el lado de baterías trabajar con polos aislados evitando este tipo de transitorios, lo cual permitiría dimensionar el convertidor DC/DC dual a los voltajes y corrientes normales de funcionamiento reduciendo peso de los convertidores y costes de fabricación de los mismos. OBJETO DE LA INVENCIÓN La presente invención proporciona una solución al problema anterior mediante un método que pre-carga y polarización del convertidor DC/DC dual para que al empezar a funcionar el convertidor DC/DC dual de forma normal, las baterías "BSS" y el campo solar fotovoltaico "PV" se encuentren al mismo voltaje respecto de tierra. La solución aportada permite a un convertidor DC/DC dual no aislado operar de forma segura y sin producir daños en una configuración de campo solar fotovoltaico "PV" con polos a tierra y baterías "BSS" flotante (polos aislados) . Es decir, la solución aportada elimina ambos transitorios por polarización que se producen en los convertidores DC/DC duales del estado de la técnica. DESCRIPCIÓN DE LA INVENCIÓN La presente invención divulga un método de polarización intrínseca de un convertidor DC/DC dual que es capaz de eliminar el transitorio de polarización al conectar el rack de baterías al bus interno del convertidor DC/DC dual y el transitorio de polarización al arrancar el convertidor DC/DC dual para su operación normal. La topología del convertidor DC/DC dual comprende, al menos, un bus interno del lado del campo solar fotovoltaico y un bus interno del lado de baterías. El bus interno del lado del campo solar fotovoltaico a su vez comprende: un primer transistor, un segundo transistor, un tercer transistor, y un cuarto transistor, conectados en serie. Adicionalmente, el bus interno del lado del campo solar fotovoltaico comprende unas resistencias y unos condensadores conectados en serie. Los transistores conectados en serie están conectados en paralelo con las resistencias y los condensadores conectados en serie. Además, el bus interno del lado del campo solar fotovoltaico es conectable con un campo solar fotovoltaico mediante unos segundos medios de cierre. Por su parte, el bus interno del lado de baterías a su vez comprende: un quinto transistor, un sexto transistor, un séptimo transistor y un octavo transistor conectados en serie. Adicionalmente, el bus interno del lado de baterías comprende unas resistencias y condensadores conectados en serie. Los transistores conectados en serie están conectados en paralelo con las resistencias y los condensadores conectados en serie. El bus interno del lado de baterías es conectable con un rack de baterías mediante unos primeros medios de cierre. Los primeros y segundos medios de cierre pueden ser contactores. Adicionalmente, los primeros medios de cierre pueden comprender una resistencia "RSC" en serie con el contactor para realizar la carga suave pasiva conocida en el estado de la técnica. El convertidor DC/DC dual puede comprender filtros RFI que filtran las frecuencias altas. Los filtros RFI conectan el bus interno del lado de baterías con tierra. Los filtros RFI pueden comprender varios condensadores y una resistencia en paralelo, y una resistencia en serie para unir el filtro con el bus interno del lado de baterías. El convertidor DC/DC dual puede comprender unos medios de control conectados con al menos: el primer transistor, el segundo transistor, el tercer transistor, el cuarto transistor, el quinto transistor, el sexto transistor, el séptimo transistor, el octavo transistor, los primeros medios de cierre, los segundos medios de cierre, donde los medios de control están configurados para llevar a cabo el método de polarización intrínseca de la presente invención que se detalla a continuación. Los medios de control pueden estar seleccionados entre un microcontrolador, un microprocesador y una FPGA. Para la topología del convertidor DC/DC dual descrito previamente, el método de polarización intrínseca de la presente invención comprende los siguientes pasos: i) conectar el convertidor DC/DC dual con el campo solar fotovoltaico cerrando los segundos medios de cierre y aislar el convertidor DC/DC del rack de baterías abriendo los primeros medios de cierre; ii) precargar el bus interno del lado de baterías al mismo voltaje respecto de tierra que tiene el rack de baterías con energía procedente del campo solar fotovoltaico mediante conmutaciones predefinidas de (todos) los transistores; iii) aislar el bus interno del lado de baterías del bus interno del lado del campo solar fotovoltaico hasta que el bus interno del lado de baterías esté polarizado igual que el rack de baterías (=pasar el bus interno del lado de baterías de modo diferencial con negativo a tierra a modo diferencial donde los lados positivos y negativos están equidistantes de tierra) , dejando abiertos los transistores del bus interno del lado del campo solar fotovoltaico; iv) conectar el bus interno del lado de baterías con el rack de baterías, cerrando los primeros medios de cierre; v) abrir el primer transistor, el cuarto transistor, el quinto transistor y el octavo transistor; i) polarizar a un voltaje respecto de tierra el bus interno del lado de baterías (y por tanto, también el rack de baterías porque están conectados) mediante conmutaciones sincronizadas del segundo transistor, del tercer transistor, del sexto transistor y del séptimo transistor donde las conmutaciones de los transistores se realizan en periodos de tiempo "T" con ciclos de trabajo crecientes en incrementos de tiempo desde un valor mínimo equivalente al tiempo de conmutación de los transistores hasta un valor máximo donde los transistores están cerrados, para que no haya transferencia de energía entre los lados internos del convertidor ya que la poca energía generada en las conmutaciones se disipará en las resistencias y bobinas que unen ambos lados internos. En una forma de realización, el paso ii) adicionalmente comprende que el convertidor DC/DC dual funcione tipo "reductor" (Buck) cuando el voltaje en el rack de baterías es inferior al voltaje en el campo solar fotovoltaico. Por tanto, las conmutaciones predefinidas del paso ii) del método de la presente invención, para que el convertidor DC/DC dual funcione tipo "reductor" (Buck) comprenden al menos: • abrir el sexto transistor y el séptimo transistor; • cerrar el quinto transistor y el octavo transistor; y, • conmutar el primer transistor, el segundo transistor, el tercer transistor, y el cuarto transistor. En una forma de realización, el paso ii) adicionalmente comprende que el convertidor DC/DC dual funcione tipo "elevador" (Boost) cuando el voltaje en el rack de baterías es superior al voltaje en el campo solar fotovoltaico. Por tanto, las conmutaciones predefinidas del paso ii) del método de la presente invención, para que el convertidor DC/DC dual funcione tipo "elevador" (Boost) comprenden al menos: • abrir el segundo transistor y el tercero transistor; • cerrar el primero transistor y el cuarto transistor; y, • conmutar el quinto transistor, el sexto transistor, el séptimo transistor y el octavo transistor. En toda la presente memoria descriptiva, se entenderá de forma equivalente los términos "batería", "baterías" y "rack de baterías". BREVE DESCRIPCIÓN DE LAS FIGURAS. Fig. 1.- Se muestra un convertidor DC/DC diferencial de tipo "dual" conectado a un campo solar fotovoltaico y a un rack de baterías. Fig.2.- Se muestra los transitorios que sufren los polos positivo y negativo del rack de baterías cuando se conecta el convertidor DC/DC dual del estado de la técnica al rack de baterías. Fig. 3.- Se muestra un convertidor DC/DC diferencial de tipo "dual" conectado a un campo solar fotovoltaico y a un rack de baterías, donde el convertidor DC/DC dual tiene una resistencia de carga suave pasiva y filtros RFI. Fig. 4.- Se muestra un diagrama de flujo del método de la presente invención. Fig. 5.- Se muestran los componentes que se activan para llevar a cabo la polarización del rack de baterías. REALIZACIÓN PREFERENTE DE LA INVENCIÓN. En la Fig. 1 se muestra un convertidor DC/DC diferencial de tipo "dual" 10 conectado a un campo solar fotovoltaico "PV" 21 y a un rack de baterías "BSS" 20. El convertidor DC/DC dual 10 tiene el bus interno del lado del campo solar fotovoltaico 11 y el bus interno del lado de baterías 12. El bus interno del lado del campo solar fotovoltaico 11 tiene el primer transistor 1B, el segundo transistor 2B, el tercer transistor 3B y el cuarto transistor 4B conectados en serie. Adicionalmente, el bus interno del lado del campo solar fotovoltaico 11 tiene la primera resistencia 1R, el primer condensador 1C, la segunda resistencia 2R y el segundo condensador 2C conectados en serie, los cuales a su vez están conectados en paralelo con los cuatro transistores 1B-4B, tal y como se muestra en la Fig. 1. En la Fig. 1 también se observa que el punto medio 14 de la rama de los cuatro transistores 1B-4B está conectado con el punto medio 13 de la rama de los condensadores y resistencias 1R-1C-2R-2C. El bus interno del lado del campo solar fotovoltaico 11 está conectado a tierra 17, lo que da lugar a la "configuración de polo a tierra" del lado del campo solar fotovoltaico 21. El bus interno del lado de baterías 12 tiene el quinto transistor 5B, el sexto transistor 6B, el séptimo transistor 7B y el octavo transistor 8B conectados en serie. Adicionalmente, el bus interno del lado de baterías 12 tiene la tercera resistencia 3R, el tercer condensador 3C, la cuarta resistencia 4R y el cuarto condensador 4C conectados en serie, los cuales a su vez están conectados en paralelo con los cuatro transistores 5B, 6B, 7B, 8B, tal y como se muestra en la Fig. 1. En la Fig. 1 también se observa que el punto medio 15 de la rama de los cuatro transistores 5B-8B está conectado con el punto medio 16 de la rama de los condensadores y resistencias 3R-3C-4R-4C. El bus interno del lado de baterías 12 no está conectado a tierra, lo que da lugar a la "configuración de polos aislados" del lado de baterías 20. Finalmente, en la Fig. 1, se puede observar que el bus interno del lado del campo solar fotovoltaico 11 y el bus interno del lado de baterías 12 están conectados entre sí por bobinas y esistencias. Concretamente, el punto de conexión 18A entre el primer transistor 1B y el segundo transistor 2B está conectado con el punto de conexión 18B entre el quinto transistor 5B y el sexto transistor 6B, mediante la primera bobina 1L y la quinta resistencia 5R. Adicionalmente, el punto de conexión 19A entre el tercer transistor 3B y el cuarto transistor 4B está conectado con el punto de conexión 19B entre el séptimo transistor 7B y el octavo transistor 8B, mediante la segunda bobina 2L y la sexta resistencia 6R. En la Fig. 2 se muestran los transitorios de polarización que sufren los polos positivo y negativo del rack de baterías cuando se conecta el convertidor DC/DC dual del estado de la técnica al rack de baterías y que no se producen al aplicar el método de la presente invención. En la Fig. 3 se muestra el convertidor DC/DC diferencial de tipo "dual" 10 de la Fig. 1 conectado al campo solar fotovoltaico 21 mediantes los contactores 27. Adicionalmente, el convertidor DC/DC dual 10 se conecta con el rack de baterías 20 mediante una configuración de carga suave formada la resistencia "RSC" 22 y los contactores 25. Y una vez terminada la carga suave, se conecta el rack de baterías 20 con el convertidor DC/DC dual mediante los contactores 26 como es conocido en el estado de la técnica. Siguiendo con la Fig. 3, también es conocido en el estado de la técnica que el bus interno del lado de baterías 12 del convertidor DC/DC dual, si bien no está conectado a tierra directamente en la configuración de "polos aislados", dicho bus interno del lado de baterías 12 sí está conectado a tierra mediante los filtros "RFI" 23 encargados de filtrar las altas frecuencias. En el caso mostrado en la Fig.3, los filtros RFI están formados por tres condensadores 23C y una resistencia 23R conectados en paralelo y por una resistencia 24 que conecta cada rama del bus interno del lado del lado de baterías 12 con tierra. Para la configuración de un convertidor DC/DC diferencial de tipo "dual" 10 como el mostrado en las figuras 1 y 3, la presente invención divulga un método de polarización intrínseca del convertidor DC/DC dual que, mediante una precarga y una polarización interna, es capaz de eliminar el transitorio de polarización al conectar las baterías al bus interno del convertidor DC/DC dual y el transitorio de polarización al arrancar el convertidor DC/DC dual para su operación normal. Por tanto, el método de la presente invención comprende realizar una precarga activa del convertidor DC/DC dual. Pero antes, el convertidor DC/DC dual 10 tiene que estar conectado al campo solar fotovoltaico "PV" 21 y desconectado del rack de baterías "BSS" 20. Es decir, los contactores 27 están cerrados y los contactores 25 y 26 de la figura 3 están abiertos. Por tanto, el primer paso del método es conectar (Fig. 4 - 30) el convertidor DC/DC dual 10 con el campo solar fotovoltaico 21 cerrando el contactor 27 y mantener aislado el convertidor DC/DC 10 del rack de baterías 20 manteniendo abiertos los contactores 25 y 26. A continuación (Fig. 4 - 31) , e lleva a cabo la precarga activa que comprende igualar de forma controlada y progresiva el voltaje interno (el voltaje de los buses internos de baterías 12 y PV 11) respecto de tierra del DC/DC dual 10 al valor de voltaje que tiene el rack de baterías 20 en modo diferencial equidistante de tierra. Por ejemplo, si el rack de baterías 20 tiene un voltaje en modo diferencial de 1000v (-500v y +500v respecto a GND) y el campo solar fotovoltaico PV 21 tiene un voltaje de 1200v en modo diferencial (entre 0v y 1200v respeto a GND) respecto a tierra, los buses internos 11 y 12 del convertidor DC/DC dual 10 se precargan a 1000v en modo diferencial (entre 0v y 1000v respecto a GND) respecto a tierra con energía procedente del campo solar fotovoltaico PV 21. Nótese que el convertidor DC/DC dual 10 es no aislado y la polarización del campo solar fotovoltaico PV coincide con la de los buses internos cuando los transistores del convertidor DC/DC conmutan. Para llevar a cabo la transferencia de potencia (energía) desde el campo solar fotovoltaico PV 21 hasta el bus interno de baterías 12, para la transferencia final al rack de baterías 20, hay que conocer el voltaje en el campo solar fotovoltaico PV 21 y el voltaje en el rack de baterías 20. Si el voltaje en el rack de baterías 20 es menor que el voltaje en el campo solar fotovoltaico PV 21 (VBSs < VPV) , el convertidor DC/DC dual 10 funcionará como un reductor 31A ("Buck") donde se abrirán el sexto transistor 6B y el séptimo transistor 7B, cerrarán el quinto transistor 5B y el octavo transistor 8B, y conmutarán todos los transistores (el primer transistor 1B, el segundo transistor 2B, el tercer transistor 3B, y el cuarto transistor 4B) del lado del campo solar fotovoltaico PV, generando en bornas de la inductancia 1L una tensión superior a la del lado de baterías a cargar para provocar el flujo de potencia. Mientras que, si el voltaje en el rack de baterías 20 es mayor que el voltaje en el campo solar fotovoltaico PV 21 (VBSS > VPV) , el convertidor DC/DC dual 10 funcionará como un elevador 31B ("Boost") . El tipo de conmutación de los transistores para el caso "elevador" será la contraria a la explicada para el caso "reductor", donde se abrirán el segundo transistor 2B y el tercero transistor 3B, cerrarán el primero transistor 1B y el cuarto transistor 4B, y conmutarán todos los transistores del lado de baterías (el quinto transistor 5B, el sexto transistor 6B, el séptimo transistor 7B y el octavo transistor 8B) . Una vez que mediante la precarga activa se consigue que el voltaje interno (el voltaje de los buses internos de baterías 12 y PV 11) del DC/DC dual 10 en modo diferencial respecto de tierra sea igual al valor de voltaje que tiene el rack de baterías 20 en modo diferencial (equidistante de tierra) , el siguiente paso del método es aislar (Fig. 4, 32) el bus interno del lado de baterías 12 del bus interno del lado del campo solar fotovoltaico PV 11 hasta que el bus interno del lado de baterías 12 esté polarizado igual que el rack de baterías 20. Es decir, aislar el bus interno del lado de baterías 12 para que de forma natural, el bus interno del lado de baterías 12 tenga el mismo voltaje tanto en modo diferencial como respecto a tierra ("GND") . Para aislar el bus interno del lado de baterías 12, el método comprende dejar abiertos los ransistores 1B, 2B, 3B y 4B del bus interno del lado del campo solar fotovoltaico 11. Siguiendo con el ejemplo anterior, el bus interno del lado de baterías 12 tendría un voltaje de 1000v en modo diferencial respecto a tierra (1000.- 0v) antes de aislar el propio bus interno del lado de baterías 12. Al aislar el bus interno del lado de baterías 12, el bus interno del lado de baterías 12 de forma natural mantiene el voltaje de 1000v en modo diferencial pero modifica su voltaje en modo común o respecto a tierra (-500v sobre GND y +500v sobre GND) . Teniendo en cuenta que el voltaje en modo diferencial "VDIFF" se define como VDIFF = V2 - Vi; y voltaje en modo común "VMC" de define como VMC = (V2 + V1) /2, el VDIFF se mantiene en 1000v, pero el voltaje en modo común "VMC" pasa de 500v (= (1000-0) /2) a 0v (= (+500+ (-500) ) /2) . A continuación, el método comprende conectar (Fig. 4, 33) el bus interno del lado de baterías 12 con el rack de baterías 20. Como el bus interno del lado de baterías 12 tiene el mismo voltaje y misma polarización que el rack de baterías 12, no se produce el transitorio de polarización que se producía en el estado de la técnica al conectar las baterías al bus interno de condensadores del convertidor DC/DC dual. Para conectar el convertidor DC/DC dual 10 de la figura 3 con el rack de baterías 12, se realiza la "carga suave" mediante el cierre de los contactores 25 y la resistencia 22 según se conoce en estado de la técnica. Posteriormente, se cierra el contactor 26. Llegados a este punto, el bus interno del lado de baterías 12 estará polarizado en modo diferencial equidistante de tierra y el bus interno del lado del campo solar fotovoltaico 11 estará polarizado en modo diferencial respecto de tierra. Siguiendo con el ejemplo anterior, el bus interno del lado de baterías 12 tendría un voltaje diferencial de 1000v, polo negativo a -500v y polo positivo a +500v, y el bus interno del lado del campo solar fotovoltaico 11 tendría un voltaje diferencial de 1000v, polo positivo a +1000v y polo negativo a 0v. Esto provocaría un transitorio al comenzar el convertidor 10 a funcionar de modo normal. Todo lo anterior se puede ejemplificar con la siguiente tabla: Tabla 1 Para evitar el transitorio de "puesta en marcha", la presente invención propone polarizar el rack de baterías 20 con el objetivo de igualar los voltajes respecto a tierra "GND" antes de entrar en operación ("ON") . La polarización consiste principalmente en conmutar los transistores de potencia en una posición que no genere traspaso de energía. Para ello, se conmutan unos transistores concretos con un ciclo de trabajo lo más pequeño posible y progresivo, pero que iguale de un modo progresivo los potenciales en ambos lados internos (11, 12) del convertidor DC/DC dual. Antes de iniciar la polarización del rack de baterías 20, es necesario abrir (Fig. 4 - 34) los transistores externos (1B, 4B, 5B, 8B) del convertidor DC/DC dual. Una vez abiertos los transistores externos (1B, 4B, 5B, 8B) , ya es posible conmutar (Fig. 4 - 35) los transistores intermedios (2B, 3B, 6B, 7B) con el menor ciclo de trabajo posible hasta que el ciclo de trabajo sea igual a "1" (Fig. 4 - 37) con incrementos de tiempo At (Fig. 4 - 36) . El ciclo de trabajo mínimo será el que permita el propio transistor en función de la tecnología con la que esté fabricado el transistor de potencia. A modo de ejemplo un tiempo entre 1-3^s puede tomarse como referencia con el empleo de transistores de tipo IGBTs. El ciclo de trabajo se incrementa de modo progresivo hasta dejar los transistores 2B, 3B, 6B, 7B cerrados, momento en el cual la polarización está completada. Esto hace que comiencen a igualarse progresivamente los voltajes de ambos lados internos (11, 12) del convertidor DC/DC dual 10 de un modo que aparte de ser muy bajo en cuanto a energía (debido a que el ciclo es el mínimo posible y se incrementa lentamente) , se ve atenuado por el filtro paso-bajo implícito de las inductancias que hay entre ambos lados internos (11, 12) del convertidor DC/DC dual 10 (camino marcado con línea discontinua en la Fig. 5 donde se dibujan unas capacidades parásitas "C" de los buses) . Los incrementos de tiempo At en el ciclo de trabajo "CT" dependerán principalmente del filtro paso-bajo implícito de las inductancias y de la tecnología de los transistores (1B-8B) de potencia y sólo deben cumplirse la condición de que no haya traspaso de energía entre ambos lados internos (11, 12) del convertidor DC/DC dual 10. A modo de ejemplo, un tiempo entre 1-3^s puede tomarse como referencia para los incrementos de tiempo At con el empleo de transistores de tipo IGBTs. A continuación se incluye una comparativa entre el funcionamiento del convertidor DC/DC dual según el estado de la técnica y el funcionamiento del mismo para la polarización del lado interno de baterías 12, y por tanto, del rack de baterías 20 cuando están ambos conectados: Tabla 2 Para llevar a cabo el método de polarización intrínseca de un convertidor DC/DC dual de la presente invención, el convertidor DC/DC dual comprende unos medios de control 28 conectados con al menos: el primer transistor, el segundo transistor, el tercer transistor, el cuarto transistor, el quinto transistor, el sexto transistor, el séptimo transistor, el octavo transistor, los primeros medios de cierre, los segundos medios de cierre. Los medios de control pueden estar seleccionados entre un microcontrolador, un microprocesador y una FPGA.

Publicaciones:

ES2953912 (17/11/2023) - A1 Solicitud de patente con informe sobre el estado de la técnica

Eventos:

En fecha 06/04/2022 se realizó Registro Instancia de Solicitud

En fecha 07/04/2022 se realizó Admisión a Trámite

En fecha 07/04/2022 se realizó 1001P_Comunicación Admisión a Trámite

En fecha 08/04/2022 se realizó Superado examen de oficio

En fecha 07/11/2022 se realizó Realizado IET

En fecha 14/11/2022 se realizó 1109P_Comunicación Traslado del IET

En fecha 17/11/2023 se realizó Publicación Solicitud

En fecha 17/11/2023 se realizó Publicación Folleto Solicitud con IET (A1)

En fecha 15/02/2024 se realizó PETEX_Petición de examen sustantivo

En fecha 04/03/2024 se realizó Validación petición y/o pago de examen sustantivo conforme

En fecha 07/03/2024 se realizó El solicitante ha contestado pero existen nuevas objeciones a la concesión de la solicitud

En fecha 07/03/2024 se realizó Elaboración de examen sustantivo

En fecha 07/03/2024 se realizó 6120P_Notificación de examen sustantivo

En fecha 13/03/2024 se realizó Publicación de examen sustantivo

Pagos:

05/04/2022 - Pago Tasas IET

Fuente de la información

Parte de la información aquí publicada es pública puesto que ha sido obtenida de la Oficina de Propiedad Industrial de los diferentes países el 29/04/2024 y por lo tanto puede ser que la información no esté actualizada.Parte de la información aquí mostrada ha sido calculada por nuestro sistema informático y puede no ser veraz.

Privacidad

Si considera que al información aquí publicada afecta a su privacidad y desea que eliminemos la información aquí publicada envíe un email a info@patentes-y-marcas.com o rellene el formulario que encontrará aquí.Información sobre el registro de patente nacional por MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL con el número P202230307

El registro de patente nacional por MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL con el número P202230307 fue solicitada el 06/04/2022. Se trata de un registro en España por lo que este registro no ofrece protección en el resto de países. El registro MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL con el número P202230307 fue solicitada por POWER ELECTRONICS ESPAÑA, S.L. mediante los servicios del agente Javier Ungría López. El registro [modality] por MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL con el número P202230307 está clasificado como H02M 3/335 según la clasificación internacional de patentes.

Otras invenciones solicitadas por POWER ELECTRONICS ESPAÑA, S.L.

Es posible conocer todas las invenciones solicitadas por POWER ELECTRONICS ESPAÑA, S.L. entre las que se encuentra el registro de patente nacional por MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL con el número P202230307. Si se desean conocer más invenciones solicitadas por POWER ELECTRONICS ESPAÑA, S.L. clicar aquí.Otras invenciones solicitadas en la clasificación internacional de patentes H02M 3/335.

Es posible conocer invenciones similares al campo de la técnica se refiere. El registro de patente nacional por MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL con el número P202230307 está clasificado con la clasificación H02M 3/335 por lo que si se desea conocer más registros con la clasificación H02M 3/335 clicar aquí.Otras invenciones solicitadas a través del representante JAVIER UNGRÍA LÓPEZ

Es posible conocer todas las invenciones solicitadas a través del agente JAVIER UNGRÍA LÓPEZ entre las que se encuentra el registro patente nacional por MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL con el número P202230307. Si se desean conocer más invenciones solicitadas a través del agente JAVIER UNGRÍA LÓPEZ clicar aquí.Patentes en España

Es posible conocer todas las invenciones publicadas en España entre las que se encuentra el registro patente nacional por MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL. Nuestro portal www.patentes-y-marcas.com ofrece acceso a las publicaciones de patentes en España. Conocer las patentes registradas en un país es importante para saber las posibilidades de fabricar, vender o explotar una invención en España.Patentes registradas en la clase H

Es posible conocer todas las patentes registradas en la clase H (ELECTRICIDAD) entre las que se encuentra la patente MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL con el número P202230307. Conocer las patentes registradas en una clase es importante para saber las posibilidades de registrar una patente en esa misma clase.Patentes registradas en la clase H02

Es posible conocer todas las patentes registradas en la clase H02 (PRODUCCION, CONVERSION O DISTRIBUCION DE LA ENERGIA ELECTRICA) entre las que se encuentra la patente MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL con el número P202230307. Conocer las patentes registradas en una clase es importante para saber las posibilidades de registrar una patente en esa misma clase.Patentes registradas en la clase H02M

Es posible conocer todas las patentes registradas en la clase H02M (APARATOS PARA LA TRANSFORMACION DE CORRIENTE ALTERNA EN CORRIENTE ALTERNA, DE CORRIENTE ALTERNA EN C) entre las que se encuentra la patente MÉTODO DE POLARIZACIÓN INTRÍNSECA DE UN CONVERTIDOR DC/DC DUAL con el número P202230307. Conocer las patentes registradas en una clase es importante para saber las posibilidades de registrar una patente en esa misma clase.

¿Tienes alguna duda?

Escribe tu consulta y te responderemos rápida y gratuitamente.

P202230305

P202230305