- Home /

- Publicaciones de patentes /

- DISPOSITIVO Y MÉTODO DE FUNCION FÍSICA NO CLONABLE (PUF) BASADA EN RUIDO TELEGRÁFICO ALEATRORIO (RTN)

Patente nacional por "DISPOSITIVO Y MÉTODO DE FUNCION FÍSICA NO CLONABLE (PUF) BASADA EN RUIDO TELEGRÁFICO ALEATRORIO (RTN)"

Este registro ha sido solicitado por

Persona física

a través del representanteÁNGEL PONS ARIÑO

Contacto

- Estado: A punto de caducar

- País:

- España

- Fecha solicitud:

- 18/04/2022

- Número solicitud:

-

P202230344

- Número publicación:

-

ES2954611

- Fecha de concesión:

-

22/03/2024

- Inventores:

-

Persona física

- Datos del titular:

-

Persona física

- Datos del representante:

-

Ángel Pons Ariño

- Clasificación Internacional de Patentes:

- H04L 9/32

- Clasificación Internacional de Patentes de la publicación:

- H04L 9/32

- Fecha de vencimiento:

Quiero registrar una patente

Reivindicaciones:

+ ES-2954611_B21.- Un método para producir una Función Física No Clonable (PUF, "Physical Unclonable Functiori") basada en Ruido Telegráfico Aleatorio (RTN, "Random Telegraph Noise") que comprende los siguientes pasos: - seleccionar un único transistor accionado por tensión (2) o un único transistor accionado por corriente (1) o un par de transistores accionados por tensión (2) o un par de transistores accionados por corriente (1) a partir de una matriz de transistores accionados por tensión (2) o transistores accionados por corriente (1) que cumplan un conjunto predefinido de criterios y de acuerdo con un reto del PUF, - polarizar el transistor accionado por tensión (2) o el transistor accionado por corriente (1) seleccionados, o el par de transistores accionados por tensión (2) o el par de transistores accionados por corriente (1) , para producir una tensión de drenador/puerta o una corriente de drenador con ruido de tipo RTN, - medir una tensión de drenador/puerta de los transistores accionados por corriente (1) o una corriente de drenador de los transistores accionados por tensión (2) durante un determinado intervalo de tiempo, - calcular una Fluctuación Máxima de Parámetros (MPF, "Maximum Parameter Fluctuation") de la tensión de drenador/puerta de cada transistor accionado por corriente (1) o de la corriente de drenador de cada transistor accionado por tensión (2) , como: siendo: - comparar el MPF calculado del transistor accionado por tensión (2) o del transistor accionado por corriente (1) con una referencia, en el caso de un único transistor accionado por tensión (2) o de un único transistor accionado por corriente (1) , o con el MPF calculado del segundo transistor accionado por tensión (2) o del segundo transistor accionado por corriente (1) en el caso de un par de transistores accionados por tensión (2) o un par de transistores accionados por corriente (1) , para obtener un resultado binario en forma de bit digital con valor "1" si el MPF del transistor accionado por tensión (2) o del transistor accionado por corriente (1) es mayor que la referencia, o, en el caso de un par de transistores accionados por tensión (2) o un par de transistores accionados por corriente (1) , si el MPF del primer transistor accionado por tensión (2) o del transistor ccionado por corriente (1) del pares mayor que el MPF del segundo transistor accionado por tensión (2) o del transistor accionado por corriente (1) , o "0" en caso contrario. - utilizar el resultado binario de la comparación como, al menos la base de, la respuesta del PUF. 2.- El método de la reivindicación 1, que comprende adicionalmente una etapa de preselección de bits previa en la que la respuesta binaria de cada transistor accionado por tensión (2) o de cada transistor accionado por corriente (1) o par de transistores accionados por tensión (2) o par de transistores accionados por corriente (1) tiene una reproducibilidad, se produce una ordenación en función de dicha reproducibilidad, y la ordenación resultante se utiliza para tomar los transistores accionados por tensión (2) o transistores accionados por corriente (1) con mayor reproducibilidad como los candidatos disponibles para el conjunto de criterios predefinidos. 3.- El método de la reivindicación 2, en el que la ordenación de acuerdo con la repetibilidad de cada transistor accionado por tensión (2) o cada transistor accionado por corriente (1) o cada par de transistores accionados por tensión (2) o cada par de transistores accionados por corriente (1) comprende: - cuando se selecciona un solo transistor accionado por tensión (2) o un solo transistor accionado por corriente (1) , se calcula una diferencia del MPF generado con respecto a un MPF de referencia, y cuando se selecciona cada par de transistores accionados por tensión (2) o cada par de transistores accionados por corriente (1) , se obtiene una diferencia del MPF generado por separado por cada transistor accionado por tensión (2) o cada transistor accionado por corriente (1) , y - los transistores accionados por tensión (2) o los transistores accionados por corriente (1) se clasifican en función de la diferencia de MPF y los que tienen valores más altos se consideran como los de mayor repetibilidad. 4.- El método de las reivindicaciones 1 a 3, en el que el mismo reto se aplica N veces con los mismos transistores accionados por tensión (2) o los mismos transistores accionados por corriente (1) y la respuesta PUF se obtiene mediante voto mayoritario entre las N comparaciones de MPF. 5.- El método de las reivindicaciones 1 a 4, en el que el mismo reto se aplica N veces con los mismos transistores accionados por tensión (2) o los mismos transistores accionados por orriente (1) para extraer uno o más bits de un conteo digital que almacena los resultados de las N comparaciones de MPF. 6.- Un dispositivo de Función Física No Clonable (PUF) basada en el Ruido Telegráfico Aleatorio (RTN) y en la tensión de drenador, que comprende: - una matriz de transistores accionados por corriente (1) , que comprende M transistores accionados por corriente (1) del mismo tipo, en el que se aplica la misma corriente en los drenadores de los transistores y la misma tensión de fuente a todos los transistores accionados por corriente (1) , - un selector de transistores (3, 4) , conectado al conjunto de transistores accionados por corriente (1) en sus drenadores, estando el selector de transistores (3, 4) configurado para seleccionar un transistor accionado por corriente (1) , - una calculadora de Fluctuación Máxima de Tensión (MVF, "Máximum Voltage Fluctuatiorí) (5) que recibe la tensión de drenador (VDmai) del transistor accionado por corriente (1) seleccionado y devuelve un MVF calculado, y, - un comparador de MPF (12) , asociado a la calculadora de MVF (5) , configurado para recibir el MVF y compararlo con una referencia, decidiendo cuál es mayor y obteniendo una respuesta de un bit, r. 7.- El dispositivo de la reivindicación 6, en el que el selector de transistores (3, 4) es un selector de transistores M:2 configurado para seleccionar dos transistores accionados por corriente (1) , y en el que el dispositivo comprende un par de calculadoras de MVF (5) , una para cada uno de los transistores accionados por corriente (1) seleccionados, que reciben la tensión de drenador (VDmai, VDmbi) de los transistores accionados por corriente (1) seleccionados y devuelven el MVF calculado (MVFm ai, MVFmbi) , y en donde el comparador de MPF (12) , asociado a las calculadoras de MVF (5) recibe los dos MVF (MVFmai, MVFmbi) de cada transistor accionado por corriente (1) y los compara, decidiendo cuál es mayor y obteniendo una respuesta, r. 8.- El dispositivo de las reivindicaciones 6 a 7, en el que la calculadora de MVF (5) comprende - un replicador de tensión (8) que recibe la señal de tensión de drenador (VDmai) y la replica, - un par de detectores de pico (9) , conectados al replicador de tensión (8) , que reciben la tensión de drenador (VDmai) estando uno de ellos configurado para detectar el máximo, y el otro para detectar el mínimo, obteniendo la señal de tensión acumulada áxima (CMAXV, "Cumulative Máximum Voltage") y mínima (CMINV, "Cumulative Mínimum Voltage") respectivamente, - un bloque sumador (10) , conectado a los detectores de picos (9) , que resta la señal mínima (CMAXV) de la señal máxima (CMINV) para obtener un valor MVF, - un bloque de muestreo y retención (11) que controla al bloque sumador (10) y se reinicia cuando t = tf , siendo CMAXV y CMINV reiniciados a un valor inicial VD (t0) al comienzo de cada intervalo de tiempo. 9.- Un dispositivo de Función Física No Clonable (PUF) basada en el Ruido Telegráfico Aleatorio (RTN) y en la corriente de drenador, que comprende - una matriz de transistores accionados por tensión (2) , que comprende M transistores accionados por tensión (2) del mismo tipo, en el que todos los transistores accionados por tensión (2) tienen aplicada la misma tensión de puerta, drenador y fuente, - un selector de transistores (3, 4) , conectado al conjunto de transistores accionados por tensión (2) en sus drenadores, estando el selector de transistores (3, 4) configurado para seleccionar un transistor accionado por tensión (2) , - una calculadora de Fluctuación Máxima de Corriente (MCF, "Máximum Current Fluctuatiorí) (6) que recibe la señal de corriente de drenador (IDmaí) del transistor accionado por tensión (2) seleccionado y devuelve un MCF calculado (MCFmai) , y, - un comparador de MPF (12) , asociado a la calculadora de MCF (6) , configurado para recibir la señal MCF y compararla con una referencia, decidiendo cuál es mayor y obteniendo una respuesta de un bit, r. 10.- El dispositivo de la reivindicación 9, en el que el selector de transistores (3, 4) es un selector de transistores M:2 configurado para seleccionar dos transistores accionados por tensión (2) , y en el que el dispositivo comprende un par de calculadoras de MCF (6) , una para cada uno de los transistores accionados por tensión (2) seleccionados, que reciben la señal de corriente de los transistores accionados por tensión (2) seleccionados (IDmai, lDmbi) y devuelven un MCF calculado (MCFm ai, MCFmbi) , y donde el comparador de MPF (12) , asociado a las calculadoras de MCF (6) recibe los dos MCF (MCFm ai, MCFmbi) de cada transistor accionado por tensión (2) y los compara, decidiendo cuál es mayor y obteniendo una respuesta, r. 11.- El dispositivo de las reivindicaciones 9 a 10, en el que las calculadoras de MCF (6) comprenden: - un replicador de corriente (7) que recibe la señal de corriente de drenador (IDmaí) y la replica, - un par de detectores de pico (9) , conectados al replicador de corriente (7) , que reciben las señales, detectando uno de ellos el máximo, y el otro el mínimo, obteniendo la señal de corriente acumulada máxima (CMAXC, "Cumulative Máximum Curnenf) y mínima (CMINC, "Cumulative Minimum Current) , respectivamente - un bloque sumador (10) , conectado a los detectores de pico (9) , que resta la señal mínima (CMINC) de la señal máxima (CMAXC) para obtener un valor de MCF, - un bloque de muestreo y retención (11) que controla al bloque sumador (10) y se reinicia en t = tf , siendo CMAXC y CMINC reiniciados a un valor inicial ID (t0) al comienzo de cada intervalo de tiempo. 12.- El dispositivo de cualquiera de las reivindicaciones 6 a 11, en el que comprende adicionalmente un módulo de preselección de bits que comprende: - un generador de direcciones (13) , conectado al selector de transistores (3, 4) , que genera iterativamente la dirección de cada transistor accionado por tensión (2) o de cada transistor accionado por corriente (1) cuando se utiliza una arquitectura no diferencial, o las direcciones de cada posible combinación de pares de transistores accionados por tensión (2) o de cada posible combinación de pares de transistores accionados por corriente (1) cuando se utiliza una arquitectura diferencial, - un evaluador de diferencias de MPF (14) , conectado a la calculadora de MCF (6) y que calcula la diferencia del MCF del transistor accionado por tensión (2) con respecto a una referencia cuando se utiliza una arquitectura no diferencial, o conectado a la calculadora de MVF (5) y que calcula la diferencia del MVF del transistor accionado por corriente (1) con respecto a una referencia cuando se utiliza una arquitectura no diferencial o conectado a las calculadoras de MCF (6) y que computa la diferencia de los valores MCF generados por separado por cada transistor accionado por tensión (2) cuando se utiliza una arquitectura diferencial, o conectado a las calculadoras de MVF (5) y que computa los valores MVF generados por separado por el transistor accionado por corriente (1) cuando se utiliza una arquitectura diferencial, - un módulo de ordenación de la diferencia de MPF (15) que ordena los transistores accionados por tensión (2) o los transistores accionados por corriente (1) , cuando se utiliza una arquitectura no diferencial, o los pares de transistores accionados por tensión (2) o los pares de transistores accionados por corriente (1) , cuando se utiliza una arquitectura diferencial, en función de los valores calculados por el evaluador de diferencias de MPF (14) , - un módulo selector (16) que elige los transistores accionados por tensión (2) o los transistores accionados por corriente (1) , cuando se utiliza una arquitectura no iferencial, o los pares de transistores accionados por tensión (2) o los pares de transistores accionados por corriente (1) , cuando se utiliza una arquitectura diferencial, con la mayor diferencia de MPF como los que satisfacen el conjunto de criterios para la aplicación de los retos al PUF, - un circuito de almacenamiento (17) que guarda las direcciones de los transistores accionados por tensión (2) o por los transistores accionados por corriente (1) que satisfacen los criterios de aplicación de los posibles retos al PUF. 13.- El dispositivo de cualquiera de las reivindicaciones 6 a 12, en el que además comprende: - un repetidor de retos (18) que aplica N veces el mismo reto c al selector de transistores (3, 4) , - un contador digital (19) que acumula las N salidas dadas por el comparador MPF (12) de las N veces que se aplica el reto c, - un módulo de voto mayoritario (20) que decide una respuesta de un bit r para el reto Ci. 14.- El dispositivo de cualquiera de las reivindicaciones 6 a 12, en el que además comprende: - un repetidor de retos (18) que aplica N veces el mismo reto c al selector de transistores (3, 4) , - un contador digital (19) que acumula las N salidas dadas por el comparador MPF (12) de las N veces que se aplica el reto c, - un selector de bits del contador (21) que obtiene uno o más bits de respuesta r a partir de un reto c.

+ ES-2954611_A11.- Un método para producir una Función Física No Clonable (PUF, "Physical Unclonable Functiori") basada en Ruido Telegráfico Aleatorio (RTN, "Random Telegraph Noise") que comprende los siguientes pasos: - seleccionar un único transistor accionado por tensión (2) o un único transistor accionado por corriente (1) o un par de transistores accionados por tensión (2) o un par de transistores accionados por corriente (1) a partir de una matriz de transistores accionados por tensión (2) o transistores accionados por corriente (1) que cumplan un conjunto predefinido de criterios y de acuerdo con un reto del PUF, - polarizar el transistor accionado por tensión (2) o el transistor accionado por corriente (1) seleccionados, o el par de transistores accionados por tensión (2) o el par de transistores accionados por corriente (1) , para producir una tensión de drenador/puerta o una corriente de drenador con ruido de tipo RTN, - medir una tensión de drenador/puerta de los transistores accionados por corriente (1) o una corriente de drenador de los transistores accionados por tensión (2) durante un determinado intervalo de tiempo, - calcular una Fluctuación Máxima de Parámetros (MPF, "Maximum Parameter Fluctuation") de la tensión de drenador/puerta de cada transistor accionado por corriente (1) o de la corriente de drenador de cada transistor accionado por tensión (2) , como: siendo: - comparar el MPF calculado del transistor accionado por tensión (2) o del transistor accionado por corriente (1) con una referencia, en el caso de un único transistor accionado por tensión (2) o de un único transistor accionado por corriente (1) , o con el MPF calculado del segundo transistor accionado por tensión (2) o del segundo transistor accionado por corriente (1) en el caso de un par de transistores accionados por tensión (2) o un par de transistores accionados por corriente (1) , para obtener un resultado binario en forma de bit digital con valor "1" si el MPF del transistor accionado por tensión (2) o del transistor accionado por corriente (1) es mayor que la referencia, o, en el caso de un par de transistores accionados por tensión (2) o un par de transistores accionados por corriente (1) , si el MPF del primer transistor accionado por tensión (2) o del transistor ccionado por corriente (1) del pares mayor que el MPF del segundo transistor accionado por tensión (2) o del transistor accionado por corriente (1) , o "0" en caso contrario. - utilizar el resultado binario de la comparación como, al menos la base de, la respuesta del PUF. 2.- El método de la reivindicación 1, que comprende adicionalmente una etapa de preselección de bits previa en la que la respuesta binaria de cada transistor accionado por tensión (2) o de cada transistor accionado por corriente (1) o par de transistores accionados por tensión (2) o par de transistores accionados por corriente (1) tiene una reproducibilidad, se produce una ordenación en función de dicha reproducibilidad, y la ordenación resultante se utiliza para tomar los transistores accionados por tensión (2) o transistores accionados por corriente (1) con mayor reproducibilidad como los candidatos disponibles para el conjunto de criterios predefinidos. 3.- El método de la reivindicación 2, en el que la ordenación de acuerdo con la repetibilidad de cada transistor accionado por tensión (2) o cada transistor accionado por corriente (1) o cada par de transistores accionados por tensión (2) o cada par de transistores accionados por corriente (1) comprende: - cuando se selecciona un solo transistor accionado por tensión (2) o un solo transistor accionado por corriente (1) , se calcula una diferencia del MPF generado con respecto a un MPF de referencia, y cuando se selecciona cada par de transistores accionados por tensión (2) o cada par de transistores accionados por corriente (1) , se obtiene una diferencia del MPF generado por separado por cada transistor accionado por tensión (2) o cada transistor accionado por corriente (1) , y - los transistores accionados por tensión (2) o los transistores accionados por corriente (1) se clasifican en función de la diferencia de MPF y los que tienen valores más altos se consideran como los de mayor repetibilidad. 4.- El método de las reivindicaciones 1 a 3, en el que el mismo reto se aplica N veces con los mismos transistores accionados por tensión (2) o los mismos transistores accionados por corriente (1) y la respuesta PUF se obtiene mediante voto mayoritario entre las N comparaciones de MPF. 5.- El método de las reivindicaciones 1 a 4, en el que el mismo reto se aplica N veces con los mismos transistores accionados por tensión (2) o los mismos transistores accionados por orriente (1) para extraer uno o más bits de un conteo digital que almacena los resultados de las N comparaciones de MPF. 6.- Un dispositivo de Función Física No Clonable (PUF) basada en el Ruido Telegráfico Aleatorio (RTN) y en la tensión de drenador, que comprende: - una matriz de transistores accionados por corriente (1) , que comprende M transistores accionados por corriente (1) del mismo tipo, en el que se aplica la misma corriente en los drenadores de los transistores y la misma tensión de fuente a todos los transistores accionados por corriente (1) , - un selector de transistores (3, 4) , conectado al conjunto de transistores accionados por corriente (1) en sus drenadores, estando el selector de transistores (3, 4) configurado para seleccionar un transistor accionado por corriente (1) , - una calculadora de Fluctuación Máxima de Tensión (MVF, "Máximum Voltage Fluctuatiorí) (5) que recibe la tensión de drenador (VDmai) del transistor accionado por corriente (1) seleccionado y devuelve un MVF calculado, y, - un comparador de MPF (12) , asociado a la calculadora de MVF (5) , configurado para recibir el MVF y compararlo con una referencia, decidiendo cuál es mayor y obteniendo una respuesta de un bit, r. 7.- El dispositivo de la reivindicación 6, en el que el selector de transistores (3, 4) es un selector de transistores M:2 configurado para seleccionar dos transistores accionados por corriente (1) , y en el que el dispositivo comprende un par de calculadoras de MVF (5) , una para cada uno de los transistores accionados por corriente (1) seleccionados, que reciben la tensión de drenador (VDmai, VDmbi) de los transistores accionados por corriente (1) seleccionados y devuelven el MVF calculado (MVFmai, MVFmbi) , y en donde el comparador de MPF (12) , asociado a las calculadoras de MVF (5) recibe los dos MVF (MVFmai, MVFmbi) de cada transistor accionado por corriente (1) y los compara, decidiendo cuál es mayor y obteniendo una respuesta, r. 8.- El dispositivo de las reivindicaciones 6 a 7, en el que la calculadora de MVF (5) comprende - un replicador de tensión (8) que recibe la señal de tensión de drenador (VDmai) y la replica, - un par de detectores de pico (9) , conectados al replicador de tensión (8) , que reciben la tensión de drenador (VDmai) estando uno de ellos configurado para detectar el máximo, y el otro para detectar el mínimo, obteniendo la señal de tensión acumulada áxima (CMAXV, "Cumulative Máximum Voltage") y mínima (CMINV, "Cumulative Mínimum Voltage") respectivamente, - un bloque sumador (10) , conectado a los detectores de picos (9) , que resta la señal mínima (CMAXV) de la señal máxima (CMINV) para obtener un valor MVF, - un bloque de muestreo y retención (11) que controla al bloque sumador (10) y se reinicia cuando t = tf, siendo CMAXV y CMINV reiniciados a un valor inicial VD (t0) al comienzo de cada intervalo de tiempo. 9.- Un dispositivo de Función Física No Clonable (PUF) basada en el Ruido Telegráfico Aleatorio (RTN) y en la corriente de drenador, que comprende - una matriz de transistores accionados por tensión (2) , que comprende M transistores accionados por tensión (2) del mismo tipo, en el que todos los transistores accionados por tensión (2) tienen aplicada la misma tensión de puerta, drenador y fuente, - un selector de transistores (3, 4) , conectado al conjunto de transistores accionados por tensión (2) en sus drenadores, estando el selector de transistores (3, 4) configurado para seleccionar un transistor accionado por tensión (2) , - una calculadora de Fluctuación Máxima de Corriente (MCF, "Máximum Current Fluctuatiorí) (6) que recibe la señal de corriente de drenador (IDmaí) del transistor accionado por tensión (2) seleccionado y devuelve un MCF calculado (MCFmai) , y, - un comparador de MPF (12) , asociado a la calculadora de MCF (6) , configurado para recibir la señal MCF y compararla con una referencia, decidiendo cuál es mayor y obteniendo una respuesta de un bit, r. 10.- El dispositivo de la reivindicación 9, en el que el selector de transistores (3, 4) es un selector de transistores M:2 configurado para seleccionar dos transistores accionados por tensión (2) , y en el que el dispositivo comprende un par de calculadoras de MCF (6) , una para cada uno de los transistores accionados por tensión (2) seleccionados, que reciben la señal de corriente de los transistores accionados por tensión (2) seleccionados (IDmai, lDmbi) y devuelven un MCF calculado (MCFmai, MCFmbi) , y donde el comparador de MPF (12) , asociado a las calculadoras de MCF (6) recibe los dos MCF (MCFmai, MCFmbi) de cada transistor accionado por tensión (2) y los compara, decidiendo cuál es mayor y obteniendo una respuesta, r. 11.- El dispositivo de las reivindicaciones 9 a 10, en el que las calculadoras de MCF (6) comprenden: - un replicador de corriente (7) que recibe la señal de corriente de drenador (IDmaí) y la replica, - un par de detectores de pico (9) , conectados al replicador de corriente (7) , que reciben las señales, detectando uno de ellos el máximo, y el otro el mínimo, obteniendo la señal de corriente acumulada máxima (CMAXC, "Cumulative Máximum Curnenf) y mínima (CMINC, "Cumulative Minimum Current) , respectivamente - un bloque sumador (10) , conectado a los detectores de pico (9) , que resta la señal mínima (CMINC) de la señal máxima (CMAXC) para obtener un valor de MCF, - un bloque de muestreo y retención (11) que controla al bloque sumador (10) y se reinicia en t = tf, siendo CMAXC y CMINC reiniciados a un valor inicial ID (t0) al comienzo de cada intervalo de tiempo. 12.- El dispositivo de cualquiera de las reivindicaciones 6 a 11, en el que comprende adicionalmente un módulo de preselección de bits que comprende: - un generador de direcciones (13) , conectado al selector de transistores (3, 4) , que genera iterativamente la dirección de cada transistor accionado por tensión (2) o de cada transistor accionado por corriente (1) cuando se utiliza una arquitectura no diferencial, o las direcciones de cada posible combinación de pares de transistores accionados por tensión (2) o de cada posible combinación de pares de transistores accionados por corriente (1) cuando se utiliza una arquitectura diferencial, - un evaluador de diferencias de MPF (14) , conectado a la calculadora de MCF (6) y que calcula la diferencia del MCF del transistor accionado por tensión (2) con respecto a una referencia cuando se utiliza una arquitectura no diferencial, o conectado a la calculadora de MVF (5) y que calcula la diferencia del MVF del transistor accionado por corriente (1) con respecto a una referencia cuando se utiliza una arquitectura no diferencial o conectado a las calculadoras de MCF (6) y que computa la diferencia de los valores MCF generados por separado por cada transistor accionado por tensión (2) cuando se utiliza una arquitectura diferencial, o conectado a las calculadoras de MVF (5) y que computa los valores MVF generados por separado por el transistor accionado por corriente (1) cuando se utiliza una arquitectura diferencial, - un módulo de ordenación de la diferencia de MPF (15) que ordena los transistores accionados por tensión (2) o los transistores accionados por corriente (1) , cuando se utiliza una arquitectura no diferencial, o los pares de transistores accionados por tensión (2) o los pares de transistores accionados por corriente (1) , cuando se utiliza una arquitectura diferencial, en función de los valores calculados por el evaluador de diferencias de MPF (14) , - un módulo selector (16) que elige los transistores accionados por tensión (2) o los transistores accionados por corriente (1) , cuando se utiliza una arquitectura no iferencial, o los pares de transistores accionados por tensión (2) o los pares de transistores accionados por corriente (1) , cuando se utiliza una arquitectura diferencial, con la mayor diferencia de MPF como los que satisfacen el conjunto de criterios para la aplicación de los retos al PUF, - un circuito de almacenamiento (17) que guarda las direcciones de los transistores accionados por tensión (2) o por los transistores accionados por corriente (1) que satisfacen los criterios de aplicación de los posibles retos al PUF. 13.- El dispositivo de cualquiera de las reivindicaciones 6 a 12, en el que además comprende: - un repetidor de retos (18) que aplica N veces el mismo reto c al selector de transistores (3, 4) , - un contador digital (19) que acumula las N salidas dadas por el comparador MPF (12) de las N veces que se aplica el reto c, - un módulo de voto mayoritario (20) que decide una respuesta de un bit r para el reto Ci. 14.- El dispositivo de cualquiera de las reivindicaciones 6 a 12, en el que además comprende: - un repetidor de retos (18) que aplica N veces el mismo reto c al selector de transistores (3, 4) , - un contador digital (19) que acumula las N salidas dadas por el comparador MPF (12) de las N veces que se aplica el reto c, - un selector de bits del contador (21) que obtiene uno o más bits de respuesta r a partir de un reto c.

Los productos y servicios protegidos por este registro son:

H04L 9/32

Descripciones:

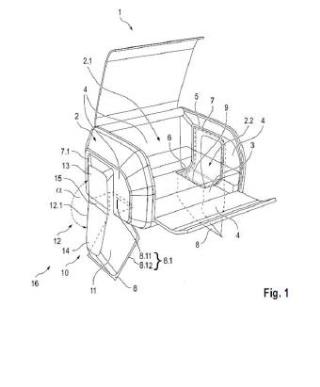

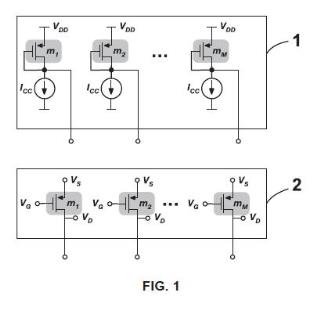

+ ES-2954611_B2 DISPOSITIVO Y MÉTODO DE FUNCIÓN FÍSICA NO CLONABLE (PUF) BASADA EN RUIDO TELEGRÁFICO ALEATORIO (RTN) OBJETO DE LA INVENCIÓN La presente invención se refiere a un método y a un dispositivo para una Función Física No Clonable (PUF, "Physical Unclonable Function") cuya fuente de entropía proviene del fenómeno conocido como ruido telegráfico aleatorio (RTN, "Random Telegraph Noise") . Se trata de un fenómeno transitorio que afecta a la tensión de umbral de los transistores en forma de cambios discretos y aleatorios. En los transistores CMOS ("complementar y metal-oxide-semiconductor") , estos cambios pueden observarse en dos escenarios: en forma de cambios de tensión en el nodo de puerta del transistor (cuando la corriente es fija) o en forma de cambios de la corriente de drenador (cuando la tensión de puerta es fija) . El origen de este fenómeno reside en la existencia de defectos en la interfaz puerta-canal del transistor y en los eventos de captura y emisión de portadores de carga en estos defectos. Tanto el número de defectos como la dinámica de las capturas/emisiones de portadores son características únicas y diferenciadoras de cada transistor, lo que significa que el fenómeno RTN puede utilizarse para generar identidades únicas a través del PUF. ANTECEDENTES DE LA INVENCIÓN En la actualidad, las memorias no volátiles (NVMs, "Non-Volatile Memories") se utilizan ampliamente como método para almacenar claves y así mantener segura la información sensible. Sin embargo, amenazas como la falsificación, la ingeniería inversa y la manipulación se están convirtiendo en serias preocupaciones para los protocolos de seguridad que utilizan NVMs, poniendo así en riesgo la información almacenada. En este escenario, las funciones físicas no clonables (PUF, "Physical Unclonable Function") surgen como alternativa a las NVMs tradicionales por su mayor resistencia a los ataques, su mayor flexibilidad y su menor coste. Se trata de una solución especialmente atractiva en aplicaciones con recursos hardware limitados como en el Internet de las Cosas (loT, "Internet of Things") , donde la potencia y el área están limitadas. Los PUFs son objetos físicos (por ejemplo, un circuito integrado) que generan una respuesta físicamente definida (salida) para un reto dado (entrada) (en lo que se llama típicamente un par reto-respuesta, CRP, "challenge-response pair1) , de una manera que es específica para la instancia concreta de hardware y que es imposible de replicar. Dicha respuesta se utiliza, por ejemplo, para autenticar cualquier objeto al que esté unida la instancia PUF o como método de identificación de un dispositivo. Así pues, las tres características fundamentales que debe cumplir un PUF son: unicidad (diferentes instancias del mismo PUF deben devolver respuestas diferentes al mismo reto) , impredecibilidad (la respuesta no puede preverse) y fiabilidad (debe obtenerse la misma respuesta para el mismo reto aplicado a la misma instancia del PUF, es decir, la respuesta del PUF debe ser robusta o estable a lo largo del tiempo y en condiciones ambientales variables) . La calidad del PUF, según estas tres características, depende, en última instancia, de la implementación específica del PUF, de su comportamiento en presencia de factores perjudiciales (como el ruido o el envejecimiento en el caso de los PUF de silicio) y del posprocesado de la respuesta. Los PUFs más utilizados en los dispositivos electrónicos son los basados en silicio, donde la aleatoriedad de la respuesta del PUF viene dada por la variabilidad en los procesos de fabricación. Entre los más conocidos están los PUFs de Osciladores en Anillo (ROs, "Ring Oscillators") , que se basan en la diferencia de frecuencia de oscilación de dos cadenas de inversores en lazo cerrado, y los PUFs de SRAM ("Static Random-Access Memor y ") , basados en el valor de encendido de las celdas de memoria (dos inversores con acoplamiento cruzado) sin escritura previa de ningún dato. Es una práctica común desarrollar algún tipo de método de preselección de bits para mejorar la fiabilidad de las respuestas en estos PUFs: en el caso de los PUFs basados en SRAM, sólo se utilizan las celdas de memoria que se encienden sistemáticamente al mismo valor y, en el caso de los PUFs basados en ROs, sólo se seleccionan como parte de la respuesta del PUF los pares de osciladores con mayores diferencias en sus frecuencias de oscilación individuales. En cualquier caso, ambas implementaciones de PUFs requieren, normalmente, un gran número de transistores para su implementación, lo que conlleva un elevado coste en área de silicio. En los dispositivos en los que las limitaciones de área son muy exigentes (por ejemplo, en los dispositivos portátiles vestibles) , esto puede ser un problema. Para reducir al máximo el área utilizada, se han propuesto PUFs cuyo fundamento es la explotación de alguna característica y la comparación de dicha característica en un par de transistores. Tanto el TCO-PUF ("Two Choses One" PUF) como el SCA-PUF ("Subthreshold Current Array PUF) son relevantes en este tipo de arquitecturas de PUF. Estos diseños utilizan la comparación del nivel de corriente de los transistores seleccionados en su región subumbral. Uno de los principales inconvenientes de estas técnicas es que la fuente de entropía no es inmune al envejecimiento viéndose afectada también por variaciones inducidas por la temperatura, pudiendo afectar gravemente a la respuesta del PUF. La solución descrita en J. Brown, "Designing, implementing, and testing hardware for cybersecurity", 2020, explota un fenómeno denominado BTI ("Bias Temperature Instability") en transistores CMOS ("Complementar y Metal-Oxide Semiconductor) . En la patente estadounidense US9794073B2, se presenta una solución que recurre al mismo fenómeno como base para el PUF. Aunque en dicho documento se menciona el mecanismo físico conocido como Ruido Telegráfico Aleatorio (RTN, "Random Telegraph Noise") , el método principal presentado se basa en la aplicación de altas tensiones de estrés en la puerta del transistor, creando así eventos de descarga BTI (en lugar de eventos RTN puros) que son realmente el núcleo del PUF propuesto. Una desventaja de estas dos técnicas es que la necesaria aplicación de fases de estrés a tensiones superiores a la nominal provoca un envejecimiento prematuro de los PUFs, lo que los hace potencialmente poco fiables con el paso del tiempo. En el trabajo presentado por M. Yoshinaga et al. ("Physically unclonable function using RTN-induced delay fluctuation in ring oscillators", ISCAS, 2016) , la respuesta del PUF se extrae de las fluctuaciones que el mecanismo RTN provoca en las frecuencias de oscilación de los ROs. Tomando dos ROs idénticos y comparando el número de fluctuaciones de frecuencia por unidad de tiempo que manifiesta cada RO como resultado de la presencia de RTN en los transistores de las cadenas de inversores, se puede obtener una respuesta. DESCRIPCIÓN DE LA INVENCIÓN La presente invención describe un método y un dispositivo para una función física no clonable (PUF, "Physical Unclonable Function") que utiliza el fenómeno del ruido telegráfico aleatorio (RTN, "Random Telegraph Noise") como fuente subyacente de entropía. Se trata de un fenómeno transitorio que se produce en la tensión de umbral de los transistores en forma de cambios discretos y aleatorios. En los transistores CMOS, puede observarse a través de dos parámetros: en forma de tensión o en forma de corriente de drenador. El origen de este fenómeno reside en la existencia de defectos en la interfaz puerta-canal del transistor y en los eventos de captura y emisión de portadores de carga en estos defectos. Los parámetros que caracterizan el fenómeno RTN son el número de defectos en el transistor, sus constantes de tiempo (el tiempo de captura (tc) y el tiempo de emisión (re) ) , y los cambios de amplitud asociados. Tanto el número de defectos como la dinámica de captura/emisión de portadores son características únicas y diferenciadoras de cada transistor, lo que significa que el fenómeno RTN puede ser potencialmente utilizado para generar identidades únicas a través del PUF. Es esencial destacar el hecho de que dos transistores idénticamente diseñados pueden mostrar diferentes cambios de la tensión umbral inducidos por el RTN. Estas variaciones entre transistores son la fuente de entropía del PUF basada en RTN de la presente invención. El elemento clave que diferencia la presente invención de otras invenciones similares que podrían utilizar este fenómeno es el hecho de que utiliza una métrica que puede condensar conjuntamente la cantidad de RTN presente en cada transistor. Comparando el valor de la métrica, denominada Fluctuación Máxima de Parámetros (MPF, "Máximum Parameter Fluctuatiorí) , bien con una referencia o bien con el valor de la misma métrica para otro transistor, se puede obtener una respuesta del PUF que puede ser utilizada, por ejemplo, para autentificar cualquier elemento hardware al que esté ligada dicha instancia del PUF. Como se ha explicado anteriormente, las fluctuaciones RTN pueden observarse tanto en la tensión en el nodo de puerta como en la corriente de drenadordel transistor. El concepto de MPF incluye ambas fluctuaciones (es decir, el parámetro observado P en la métrica MPF puede ser la tensión o la corriente de drenador) . Para observar las fluctuaciones inducidas por el RTN, se mide la corriente de drenador o se puede utilizar un método de corriente constante para obtener las fluctuaciones de tensión en el nodo de puerta. Este método consiste en utilizar una fuente de corriente, Icc, en el drenador del transistor, cortocircuitar los nodos de puerta y drenador (en una configuración de diodo convencional) y observar las fluctuaciones inducidas por el RTN en la tensión del nodo de drenador, (que equivale, en este caso, al nodo de puerta) . Durante un determinado intervalo de tiempo, definido por t0 < t' < tf, es posible calcular el Parámetro Máximo Acumulado (CMAXP, "Cumulative Máximum Parameter) . La Tensión Máxima Acumulada (CMAXV, "Cumulative Maximum Voltage") , para la tensión, y la Corriente Máxima Acumulada (CMAXC, "Cumulative Maximum Currenf) , para la corriente de drenador, pueden definirse como: Del mismo modo, la tensión mínima acumulada (CMINV, "Cumulative Mínimum Voltage) , y la corriente mínima acumulada (CMINC, "Cumulative Mínimum Current) , pueden definirse como sigue: El MPF en el instante t ' se define entonces como la diferencia entre CMAXP ( t ') (ya sea CMAXV ( t ') o CMAXC (t') ) y CMINP ( t ') (ya sea CMINV ( t ') o CMINC (t') ) : En otras palabras, el valor del MPF estará determinado por el impacto acumulado del RTN en la tensión de drenador del transistor o de la corriente del transistor (ambos relacionados con los cambios en la tensión umbral) debido a los eventos de emisión/captura observados en un intervalo de tiempo. El MPF es una función continua del tiempo, pero para llevar a cabo la comparación necesaria en el PUF, solo se utilizará el valor del MPF al final del intervalo de tiempo (tf ) La métrica MPF es una función no negativa y siempre creciente que, con el tiempo, condensa todas las variaciones inducidas por la RTN tanto en la tensión como en la corriente de drenador (reflejando el número de defectos, los cambios de amplitud causados porcada defecto, así como sus características temporales) . Por lo tanto, el uso del MPF para comparar dos transistores proporciona una forma de explotar plenamente el RTN como fuente de entropía. Además, la métrica MPF es insensible a las variaciones en la tensión umbral inducidas por el desapareamiento (ya que sólo intervienen las diferencias entre CMINP y CMAXP) , por lo que la única entropía que se emplea es la procedente del RTN. Esta es una ventaja potencial respecto a los PUFs con entropía procedente de las variaciones estáticas (es decir, a tiempo cero) , ya que éstas se ven ciertamente afectadas por el envejecimiento. El método y el dispositivo propuestos para el PUF pueden utilizar una arquitectura en la que el MPF de un solo transistor se compara con una referencia MPF. También es posible una arquitectura diferencial, en la que el cálculo del MPF se realiza en un par de transistores y luego se compara. Ambas opciones arquitecturales pueden utilizarse siendo P la tensión o la corriente. La ventaja de utilizar arquitecturas diferenciales sobre las no diferenciales es que el diseño diferencial puede mitigar y anular, en primera aproximación, las dependencias ambientales, omo el envejecimiento, la temperatura y la tensión de alimentación, ya que éstas deberían afectar a las dos estructuras idénticas de forma similar. En un primer aspecto de la invención (arquitectura no diferencial) , se selecciona un único transistor ma, especificado por el reto c (que define la dirección en la matriz del transistor específico seleccionado y que se utiliza como entrada del PUF) , de una matriz de M transistores diseñados idénticos (mismo tipo y tamaño) , utilizando un multiplexor M:1. En este caso, el elemento central del PUF es un solo transistor. Todos los transistores deben tener las mismas condiciones de polarización. Una vez seleccionado el transistor, se utiliza el parámetro elegido (ya sea tensión o corriente) en el módulo de cálculo del MPF, donde se calcula el MPF para un intervalo de tiempo preestablecido tMPF. A continuación, el resultado se compara con una MPF de referencia, determinando una salida: si MPFma > MPFre f, la salida dada es "1" ("0", en caso contrario) . Esta salida puede utilizarse como, al menos la base de, la respuesta r del PUF. Para obtener una respuesta de n bits R = (r1, r2.- , r n) , se suministra al dispositivo PUF una secuencia de n retos C = (c1; c2.- , cn) . Alternativamente, un segundo aspecto de la invención (arquitectura diferencial) , parte de una matriz con un número par M de transistores, diseñados y polarizados de forma idéntica. En este caso, el elemento central del PUF es un par de transistores ma ym b, especificado por el reto c (ahora, este reto c especifica las direcciones, en la matriz de transistores, del par seleccionado) , que se selecciona utilizando un multiplexor M:2. Una vez seleccionado el par, se utilizan los parámetros elegidos (ya sea la tensión o la corriente de cada transistor) en el módulo de cálculo del MPF. Los resultados, MPFma y MPFmb, se comparan para decidir cuál es mayor, determinando así una salida: si MPFma > MPFmb, la salida dada es "1" ("0", en caso contrario) . Esta salida puede utilizarse como, al menos la base de, la respuesta r del PUF. Para obtener una respuesta de n bits R = (r1, r2, ..., rn) , se suministra al dispositivo PUF una secuencia de n retóse = (c1, c2, ^, c n) . En resumen, el reto c puede ser una sola palabra digital a para la arquitectura no diferencial o un par de palabras digitales a y ó para la arquitectura diferencial, que seleccionan un transistor específico ma o un par específico de transistores {ma, m b}, respectivamente, de donde, se obtiene la correspondiente respuesta de un solo bit r ("0" o "1") . La función que hace corresponder un reto a una respuesta es, por tanto, la diferencia de cantidad de RTN capturada durante un determinado intervalo de tiempo, ya sea como diferencia respecto a la referencia o entre los dos transistores, siendo esta cantidad medida por el MPF. Para obtener una respuesta e n bits R = (rí, r2, ..., rn) , se suministra al dispositivo PUF una secuencia de n retos C = Un parámetro relevante en estas arquitecturas (tanto en la no diferencial como en la diferencial) es la duración del intervalo de tiempo utilizado para calcular el MPF, tMPF = tr - t 0. Cuanto más largo sea este intervalo, más eventos de emisión/captura de RTN se pueden capturar en la métrica MPF, pero, por otro lado, más tiempo tarda el dispositivo PUF en devolver una respuesta de n bits. Un intervalo de tiempo demasiado corto también puede ser problemático, ya que puede que no se observe RTN. En este sentido, una restricción adicional en el valor mínimo de tMPF resulta de considerar las constantes de tiempo de los defectos de la RTN y la capacidad del módulo de cálculo del MPF en la captura de eventos rápidos RTN, ya que cualquier tiempo de emisión tei o tiempo de captura tci por debajo del umbral de detección será ignorado. Dado que este PUF se basa en el RTN, que es único e impredecible para cada transistor, cabe esperar que el dispositivo PUF propuesto tenga también una respuesta única e impredecible. No obstante, el RTN es un fenómeno variable en el tiempo. De un uso a otro del PUF, existe la probabilidad de que un bit de respuesta cambie (de la misma manera que puede hacerlo debido a las variaciones de temperatura y a la degradación inducida por el envejecimiento) . Sin embargo, el uso de la métrica MPF disminuye la probabilidad de un cambio del bit, ya que el MPF no representa más que RTN acumulado y, por tanto, se espera que siga siendo similar en diferentes aplicaciones del mismo reto. A pesar de ello, la repetibilidad de la respuesta a un mismo reto con respecto a factores como el tiempo o la temperatura puede mejorarse aún más (minimizando así la probabilidad de que se produzca un cambio de bit) utilizando un método de preselección de bits después del proceso de fabricación del PUF. El método de preselección de bits evalúa y ordena la repetibilidad de cada bit (es decir, la repetibilidad de la respuesta de cada transistor, en la arquitectura no diferencial, o de cada par de transistores, en la arquitectura diferencial) y la ordenación resultante se utiliza para seleccionar sólo los bits más estables entre los disponibles para formar el PUF. El método de preselección de bits puede llevarse a cabo tanto para la tensión como para la corriente como parámetro elegido. La repetibilidad de la respuesta de cada transistor (cuando se compara con una referencia) o de cada par de transistores, se mide comparando el MPF de los transistores L veces consecutivas, siendo cada respuesta un "0" o un "1". Entonces, la probabilidad (P) se define como: donde n0 y n1 son el número de ceros y de unos, respectivamente, obtenidos en el conjunto de respuestas L. La repetibilidad ideal de los bits de respuesta es cuando P = 1, cuyo significado s que el bit de respuesta, a partir de la comparación del MPF (del transistor con una referencia o de los dos transistores del par) , sería siempre "1" o "0". Por tanto, un PUF formado por estos transistores o pares de transistores con P = lsería altamente fiable. Alternativamente, cuando el método de preselección de bits no es capaz de identificar bits con alta probabilidad, se pueden utilizar estructuras de tipo contador, que pueden devolver respuestas más fiables a costa de aumentar el tiempo de respuesta del PUF. Así, se puede tener una implementación basada en un voto mayoritario y/o una implementación en la que sólo se eligen aquellos bits del contador que proporcionan una mejor calidad al PUF, pudiéndose también obtener más de un bit en un solo reto. La invención descrita que incluye la arquitectura no diferencial y la diferencial (ya sea en términos de tensión o de corriente) tiene las siguientes ventajas: - minimiza el área utilizada para su implementación, en comparación con otros dispositivos PUF, ya que sólo requiere un transistor en la arquitectura no diferencial y dos transistores (un par) en la arquitectura diferencial para obtener una respuesta de un bit, - su consumo de energía es reducido, ya que para calcular la métrica MPF de los transistores, se puede polarizar éstos a tensiones muy inferiores a la tensión nominal de la tecnología, en los regímenes subumbral o lineal, - la utilización del RTN reduce el impacto de otras fuentes de variabilidad, ya que se utilizan tensiones muy inferiores a la tensión nominal de la tecnología, - el uso de una arquitectura diferencial aumenta la fiabilidad de la respuesta del dispositivo PUF en presencia de variaciones en las condiciones ambientales (envejecimiento, temperatura y cambios en las tensiones de alimentación) . DESCRIPCIÓN DE LAS FIGURAS Para complementar la descripción realizada y ayudar a una mejor comprensión de las características de la invención, de acuerdo con un ejemplo preferido de realización práctica de la misma, se adjunta como parte integrante de dicha descripción un juego de dibujos donde, con carácter ilustrativo y no limitativo, se ha representado lo siguiente: Figura 1.- Muestra la matriz de transistores accionados por corriente que puede utilizarse para la monitorización de la tensión y la matriz de transistores accionados por tensión que puede utilizarse para la monitorización de la corriente. Figura 2.- Muestra el esquema de obtención de la respuesta del PUF cuando la comparación es entre un transistor y una referencia (arquitectura no diferencial) . Figura 3.- Muestra el esquema de obtención de la respuesta del PUF cuando la comparación es entre dos transistores (arquitectura diferencial) . Figura 4.- Muestra un esquema de uso del PUF con predeterminación de transistores. Figura 5.- Muestra un esquema de uso del PUF con preselección de bits. Figura 6.- Muestra un esquema del método de preselección de bits. Figura 7.- Muestra un esquema del método para la mejora de las características del dispositivo PUF utilizando métodos basados en conteo digital. Figura 8.- Muestra un esquema de la arquitectura no diferencial, utilizando la tensión como parámetro de medida, del dispositivo PUF basado en RTN. Figura 9.- Muestra un esquema de la arquitectura no diferencial, utilizando la corriente como parámetro de medida, del dispositivo PUF basado en RTN. Figura 10.- Muestra un esquema de la arquitectura diferencial, utilizando la tensión como parámetro de medida, del dispositivo PUF basado en RTN. Figura 11.- Muestra un esquema de la arquitectura diferencial, utilizando la corriente como parámetro de medida, del dispositivo PUF basado en RTN. Figura 12.- Muestra un esquema del módulo de preselección de bits del dispositivo. Figura 13.- Muestra un esquema del módulo para la mejora de las características del PUF utilizando estructuras de tipo contador digital. REALIZACIÓN PREFERENTE DE LA INVENCIÓN A continuación, se describen, con ayuda de las Figuras 1 a 13, las realizaciones preferentes del dispositivo de función física no clonable (PUF, "Physical Unclonable Functiori") basado en el ruido elegráfico aleatorio (RTN, "Random Telegraph Noise) , así como el método objeto de la invención. Como se ha explicado anteriormente, todos los PUFs requieren de una fuente de entropía. En el caso de esta invención, la fuente utilizada es el RTN a través de la métrica MPF ("Máximum Parameter Fluctuation") . El RTN es un fenómeno transitorio que se produce en la tensión umbral de los transistores en forma de cambios discretos y aleatorios. En los transistores CMOS ("Complementar y Metal-oxide Semiconductor) , estos desplazamientos pueden observarse en dos escenarios: en forma de cambios de tensión en el nodo de puerta del transistor (cuando la corriente es fija) o en forma de cambios de la corriente de drenador (cuando la tensión de puerta es fija) . Esto se muestra en la Figura 1, con la configuración de transistores accionados por corriente (1) que se utilizan cuando se monitoriza la tensión o transistores accionados por tensión (2) que se utilizan cuando se monitoriza la corriente. El origen de este fenómeno reside en la existencia de defectos en la interfaz puerta-canal del transistor y en los eventos de captura y emisión de portadores de carga en estos defectos. El RTN, por tanto, se caracteriza por dichos defectos en el canal, las amplitudes de los cambios y los tiempos de emisión/captura de las cargas que tienen su efecto en la ocurrencia temporal de los cambios. Como elemento que condensa toda esta información y que es el relevante para la respuesta del dispositivo PUF, se utilizará el concepto de Fluctuación Máxima de Parámetro (MPF) . Este concepto puede tomar la forma de una corriente, en lo que se conoce como Fluctuación Máxima de Corriente (MCF, "Maximum Current Fluctuation") , o puede tomar la forma de una tensión, lo que se denomina Fluctuación Máxima de Tensión (MVF, "Maximum Voltage Fluctuation") . En esencia, el MPF es la diferencia entre el valor máximo del parámetro (tensión o corriente) y el mínimo durante un intervalo de tiempo. Dado que el MPF puede capturar toda la información relevante del RTN y esta información es única para cada transistor, es posible utilizar el RTN como fuente de entropía y explotarlo en el diseño de un dispositivo PUF. La Figura 2 muestra un esquema para una arquitectura general (es decir, modo de medición de tensión o corriente) no diferencial, SCH.2. La Figura 3 muestra el esquema para una arquitectura diferencial, SCH.3. Para explotar el RTN en el diseño de un PUF, en un primer paso del método objeto de la presente invención, se selecciona, según el reto c, bien un único transistor accionado por tensión (2) o n transistor accionado por corriente (1) , mostrado en SCH. 2 de la Figura 2, o bien un par de transistores accionados por tensión (2) o un par de transistores accionados por corriente (1) , mostrado en SCH. 3 de la Figura 3, y se polarizan a tensiones o corrientes bajas, suficientes para producir corrientes o tensiones con ruido de tipo RTN. La ventaja de utilizar RTN es que la polarización puede establecerse de forma que se reduzca el impacto de los fenómenos de envejecimiento, mientras que el RTN sea visible. En un segundo paso, se mide una tensión de drenador/puerta de los transistores accionados por corriente (1) o una corriente de drenador de los transistores accionados por tensión (2) durante un determinado intervalo de tiempo. En un tercer paso, se calcula el MPF para cada transistor accionado por tensión (2) o para cada transistor accionado por corriente (1) , como: siendo: donde PD representa bien la tensión de drenador o bien la corriente de drenador ID. Cuando se mide la tensión de drenador/puerta, el MPF obtenido es el MVF (Fluctuación máxima de tensión) . Cuando se mide la corriente de drenador, el MPF es el MCF (Fluctuación máxima de corriente) . En un cuarto paso, el MPF calculado del transistor accionado por tensión (2) o del transistor accionado por corriente (1) se compara con una referencia, en el caso de un único transistor accionado por tensión (2) o de un transistor accionado por corriente (1) , como se muestra en la Figura 2, o con el MPF calculado del segundo transistor en el caso de un par de transistores accionados por tensión (2) o par de transistores accionados por corriente (1) , como se muestra en la Figura 3. A continuación, para generar n respuestas PUF, se produce una secuencia de retos C = (c1; c2.- , cn) donde cada uno de los transistores accionados por tensión (2) o de los transistores ccionados por corriente (1) en cada reto c de C se asigna a la posición que ocupan en la matriz (filas y columnas) . A continuación, cada uno de los retos c de C pasa por los flujos de la SCH.2 de la Figura 2 (en el caso de transistores individuales accionados por tensión (2) o de los transistores accionados por corriente (1) ) o SCH.3 de la Figura 3 (para pares de transistores accionados por tensión (2) o pares de transistores accionados por corriente (1) ) para generar así n respuestas del PUF. El método comprende un paso previo adicional (ya sea utilizando el esquema SCH.2 de la Figura 2 o el esquema SCH. 3 de la Figura 3) que se muestra en la Figura 4 para definir los posibles retos que se aplicarán a SCH.2/SCH.3. Para ello se parte de un conjunto de criterios que por ejemplo, puede ser utilizar todos los transistores del conjunto de transistores accionados por tensión (2) o los transistores accionados por corriente (1) , o incluso, sólo un subconjunto de ellos, o bien utilizar sólo pares de transistores adyacentes accionados por tensión (2) o pares de transistores accionados por corriente (1) . Todos los transistores accionados por tensión (2) o por corriente (1) , al igual que pares de transistores accionados por tensión (2) o por corriente (1) que cumplan estos criterios, y que, por lo tanto, están disponibles para formar un reto c son predeterminados. Este reto c indica un transistor específico accionado por tensión (2) o por corriente (1.- para la arquitectura no diferencial- o un par de transistores accionados por tensión (2) o por corriente (1) para la arquitectura diferencial. Para mejorar aún más la fiabilidad del método, éste puede comprender una etapa de preselección de bits, en la que se ordena la repetibilidad de cada bit (es decir, la repetibilidad de la respuesta de cada transistor accionado por tensión (2) o de cada transistor accionado por corriente (1) o de cada par de transistores accionados por tensión (2) o de cada par de transistores accionados por corriente (1) ) y la ordenación resultante se utiliza para seleccionar sólo los bits más estables entre los disponibles para formar el PUF. Como se describe en la Figura 5, a partir del conjunto de criterios inicial, el conjunto de retos disponibles c pasa por un proceso de preselección. El paso de preselección de bits puede llevarse a cabo tanto para las arquitecturas no diferenciales como para las diferenciales (además, el parámetro elegido puede ser tensión o de corriente) . Una ordenación eficiente en función de la repetibilidad para el proceso de preselección de bits en la Figura 5 se basa en la evaluación de la diferencia del MPF, como se ilustra en la Figura 6. Para la arquitectura no diferencial en la que se selecciona un solo transistor accionado por tensión (2) o un solo transistor accionado por corriente (1) , se evalúa la diferencia del MPF generado con respecto al MPF de referencia. Para la arquitectura diferencial en la que se elecciona un par de transistores accionados por tensión (2) o un par de transistores accionados por corriente (1) , se evalúa la diferencia del MPF generado por separado por cada transistor accionado por tensión (2) o cada transistor accionado por corriente (1) . En ambos casos, se ordenan en función de la diferencia de MPF y se seleccionan los retos que cumplen un determinado criterio (por ejemplo, los que han generado la mayor diferencia en valor absoluto, o los que, habiendo calculado la diferencia de MPF un determinado número de veces, producen los resultados más homogéneos) . El conjunto resultante de retos c* es utilizado por un generador de retos para generar una secuencia de retos C que producirá una respuesta de una longitud determinada del dispositivo PUF cuando sea procesado por el SCH.2 o SCH.3 (un único transistor accionado por tensión (2) o un único transistor accionado por corriente (1) o un par de transistores accionados por tensión (2) o un par de transistores accionados por corriente (1) , respectivamente) . Por lo tanto, un PUF hecho de transistores accionados por tensión (2) o transistores accionados por corriente (1) o por pares de transistores accionados por tensión (2) o pares de transistores accionados por corriente (1) con alta repetibilidad, sería altamente fiable. La fiabilidad del PUF también puede mejorarse (tanto si se lleva a cabo una preselección de bits como si no, y tanto para las arquitecturas diferenciales como para las no diferenciales) con los métodos ilustrados en la Figura 7, en los que un mismo reto c se repite N veces con los mismos transistores accionados por tensión (2) o los mismos transistores accionados por corriente (1) (esto incluye los esquemas SCH.2 y SCH.3) y que utiliza un conteo digital. Así, se puede tener una implementación del método basada en un voto mayoritario y/o otra implementación del método en la que sólo se seleccionan ciertos bits del resultado del conteo digital que proporcionen una mejor calidad al PUF. Las flechas discontinuas indican la posibilidad de implementar cualquiera de los dos métodos (voto mayoritario o selección de bits del conteo digital) , así como ambos simultáneamente. El método expuesto, que incluye el cálculo del MPF, la comparación del MPF, el método de preselección de bits y las estructuras basadas en conteo digital, pueden implementarse con una circuitería de propósito especial o calcularse utilizando un procesador electrónico, ya sea externo o que coexista, en el mismo circuito integrado, con la matriz de transistores accionados por tensión (2) o transistores accionados por corriente (1) . A continuación, se describen dos realizaciones del mencionado circuito de propósito especial para el cálculo del MPF y la comparación del MPF, junto con el conjunto de transistores ccionados por tensión (2) y transistores accionados por corriente (1) así como su mecanismo de selección. La Figura 2 muestra un esquema para la arquitectura general (es decir, modo de medición de tensión o corriente) no diferencial, SCH.2. Las correspondientes implementaciones arquitecturales (para las mediciones de tensión y corriente, respectivamente) de la primera realización de la invención se muestran en los esquemas de las Figuras 8 y 9. El funcionamiento del dispositivo de la invención es el siguiente. Partiendo de una matriz de transistores accionados por tensión (2) o transistores accionados por corriente (1) , todos ellos del mismo tipo (NMOS o PMOS") y tamaño, organizados en una matriz de filas y columnas (en la que se puede utilizar una palabra digital para identificar la fila y la columna que cada transistor accionado por tensión (2) o cada transistor accionado por corriente (1) ocupa en la matriz) , la idea es comparar el MPF de un transistor accionado por tensión (2) o de un transistor accionado por corriente (1) con una referencia y, dependiendo de cuál sea mayor, obtener 0 o 1 lógico como respuesta. En esta primera realización, el dispositivo comprende: - Una matriz de transistores accionados por tensión (2) o transistores accionados por corriente (1) , que comprende M transistores accionados por tensión (2) o M transistores accionados por corriente (1) , del mismo tipo y diseñados de la misma manera. Para todos los transistores accionados por corriente (1) de la Figura 8, la configuración requiere que se aplique la misma corriente Icc y la misma tensión de fuente, mientras que a todos los transistores accionados por tensión (2) de la Figura 9 se les debe aplicar la misma tensión de puerta, drenador y fuente. - Un selector de transistores (3, 4) , realizado mediante un multiplexor M:1. El selector de transistores (3, 4) se conecta al conjunto de transistores accionados por tensión (2) o al conjunto de transistores accionados por corriente (1) en sus drenadores. Éste recibe un reto, c (representando al transistor accionado por tensión (2) específico o al transistor accionado por corriente (1) específico, seleccionado para ser utilizado como entrada al PUF) , que determina qué transistor accionado por tensión (2) o qué transistor accionado por corriente (1) (mediante una palabra digital {a} que especifica la dirección en la matriz de transistores accionados por tensión (2) o transistores accionados por corriente (1) del transistor accionado por tensión (2) o transistor accionado por corriente (1) específico que debe ser seleccionado por el selector de transistores (3, 4) ) para realizar la comparación de MPFs. El selector de transistores (3, 4) lo selecciona y, se utiliza o bien la tensión de renador (Figura 8) o bien la corriente de drenador (Figura 9) en la siguiente etapa. De cada transistor accionado por tensión (2) seleccionado, o cada transistor accionado por corriente (1) seleccionado, se puede obtener un bit como respuesta. - Una calculadora de MPF (una calculadora de MVF (5) en el caso de la Figura 8, y una calculadora de MCF (6) en el caso de la Figura 9) que recibe la tensión de drenador del transistor accionado por corriente (1) seleccionado (VDmai) o la señal de corriente de drenador del transistor accionado por tensión (2) seleccionado (IDmaí) Al final del proceso, la calculadora de MPF devuelve el valor del MPF calculado (MVFmai en la Figura 8 o MCFmai en la Figura 9) . Además, la calculadora de MPF comprende: o Un replicador de corriente (7) que recibe la señal de corriente y la replica (Figura 9) o un replicador de tensión (8) que recibe la señal de tensión y la replica (Figura 8) . o Un par de detectores de picos (9) , conectados al replicador de corriente (7) (Figura 9) o al replicador de tensión (8) (Figura 8) , que reciben las señales. Uno de ellos detecta el máximo, mientras que el otro detecta el mínimo, obteniendo la señal de parámetro (tensión o corriente) acumulada máxima (CMAXP, "Cumulatitve Máximum Parameter") y mínima (CMINP, "Cumulatitve Mínimum Parameter") respectivamente. o Un bloque sumador (10) , conectado a los detectores de picos (9) , que resta la señal mínima de la máxima para obtener el valor del MPF (bien el MVF, en la Figura 8, o el MCF, en la Figura 9) . o Un bloque de muestreo y retención (11) que controla el bloque sumador (10) y se reinicia en t = tf, asegurando que el cálculo de MPF se realiza en cada intervalo de tiempo, tMPF (tMVF o tMCF) . Al principio de este intervalo de tiempo, tanto CMAXP como CMINP se restablecen a los valores iniciales (en los que CMAXP = CMINP = VD (t0) | /D ( t0) ) . Así, se puede obtener un MPF diferente en cada intervalo de tiempo tMPF. - Un comparador de MPF (12) , asociado a la calculadora de MPF (una calculadora de MVF (5) para la Figura 8, y una calculadora de MCF (6) para la Figura 9) . Recibe la señal de MPF del transistor accionado por tensión (2) o del transistor accionado por corriente (1) y la compara con una referencia, decidiendo cuál es mayor y obteniendo una respuesta de un bit, ri. La Figura 3 muestra el esquema de la arquitectura diferencial, SCH.3. De forma correspondiente, en esta segunda realización de la invención, la Figura 10 y la Figura 11 uestran un esquema del dispositivo PUF propuesto basado en una arquitectura diferencial (en términos de tensión (Figura 10) y corriente (Figura 11) , respectivamente) . El funcionamiento del dispositivo de la invención es el siguiente. Partiendo de los transistores accionados por tensión (2) o de los transistores accionados por corriente (1) , todos ellos del mismo tipo y tamaño, organizados en una matriz de filas y columnas, se trata de comparar el MPF de dos transistores accionados por tensión (2) o de dos transistores accionados por corriente (1) y dependiendo de cuál sea mayor, obtener la respuesta como un 0 o un 1 lógico. En esta segunda realización, el dispositivo comprende: - Una matriz de transistores accionados por tensión (2) o de transistores accionados por corriente (1) , que comprende M transistores accionados por tensión (2) o M transistores accionados por corriente (1) , del mismo tipo y diseñados de la misma manera, que se utilizarán para formar pares. Para todos los transistores accionados por corriente (1) de la Figura 10 la configuración requiere que se aplique la misma corriente Icc y la misma tensión de fuente, mientras que a todos los transistores accionados por tensión (2) de la Figura 11 se les debe aplicar la misma tensión de puerta, drenador y fuente. - Un selector de transistores (3, 4) , realizado por un multiplexor M:2. El selector de transistores (3, 4) está conectado a los drenadores de los transistores accionados por tensión (2) o a los drenadores de los transistores accionado por corriente (1) . Éste recibe un reto, c, (representando a los transistores accionados por tensión (2) específicos o los transistores accionados por corriente (1) específicos seleccionados para ser utilizados como entrada del PUF) que determina qué dos transistores accionados por tensión (2) o que dos transistores accionados por corriente (1) (mediante las palabras digitales (a, 6] que especifican la dirección en la matriz de transistores accionados por tensión (2) o de transistores accionados por corriente (1) de los transistores accionados por tensión (2) específicos o de los transistores accionados por corriente (1) específicos que deben ser seleccionados por el selector de transistores (3, 4) ) para realizar la comparación de MPF. El selector de transistores (3, 4) los selecciona y, se utiliza o bien la tensión de drenador (Figura 10) o bien la corriente de drenador (Figura 11) en la siguiente etapa. De cada par seleccionado se puede obtener un bit como respuesta. - Un par de calculadoras de MPF (calculadoras de MVF (5) para la Figura 10, y calculadoras de MCF (6) para la Figura 11) , uno para cada uno de los transistores seleccionados accionados por tensión (2) o para cada uno de los transistores accionados por corriente (1) . Reciben la señal de tensión de drenador de los transistores accionados por corriente (1) seleccionados (VDmai o VDmbi) o la señal de corriente de drenador de los transistores accionados por tensión (2) seleccionados (IDmai o lDmbi) . Al final del roceso, se devuelve el MPF calculado (ya sea MVFmai o MVFmbi, en la Figura 10, o MCFmai o MCFmbi, en la Figura 11) . Además, cada una de las calculadoras de MPF comprende: o Un replicador de corriente (7) que recibe la señal de corriente y la replica (Figura 11) o un replicador de tensión (8) que recibe la señal de tensión y la replica (Figura 10) . o Un par de detectores de picos (9) , conectados al replicador de corriente (7) (Figura 11) o al replicador de tensión (8) (Figura 10) que reciben la señal. Uno de ellos detecta el máximo, mientras que el otro detecta el mínimo, obteniendo el máximo (CMAXP) y el mínimo (CMINP) . o Un bloque sumador (10) , conectado a los detectores de picos (9) , que resta la señal mínima de la máxima para obtener el valor del MPF. o Un bloque de muestreo y retención (11) que controla el bloque sumador (10) y se reinicia en t = tf, asegurando que el cálculo de MPF se realiza en cada intervalo de tiempo, tMPF. Al principio de este intervalo de tiempo, tanto CMAXP como CMIN CMINP P se restablecen a los valores iniciales (en los que CMAXP = CMINP = VD (t0) | /D ( t0) ) . Así, se puede obtener un MPF diferente en cada intervalo de tiempo tMPF. - Un comparador de MPF (12) , asociado a las calculadoras de MPF (calculadoras de MVF (5) para la Figura 10, y calculadoras de MCF (6) para la Figura 11) . Recibe las dos señales MPF de cada uno de los transistores accionados por tensión (2) o de cada uno de los transistores accionados por corriente (1) y las compara, decidiendo cuál es mayor y obteniendo una respuesta de un bit, r. Esta segunda realización presenta una arquitectura diferencial que tiene la ventaja, en comparación con una no diferencial, de una mayor robustez frente al envejecimiento, así como frente a las variaciones de temperatura y/o de tensión de alimentación, ya que los transistores accionados por tensión (2) o los transistores accionados por corriente (1) se ven igualmente afectados, y el efecto perjudicial se anula. Por lo tanto, esta realización no sólo implementa la robustez contra los cambios en las condiciones ambientales de uso, sino también un doble mecanismo de seguridad en términos de envejecimiento (el uso de RTN, que se considera en gran medida insensible al envejecimiento, junto con una arquitectura diferencial) . A continuación, se describe una realización que implementa el método de preselección de bits de la Figura 6 que puede utilizarse para mejorar la fiabilidad de las dos realizaciones del PUF descritas anteriormente. En esta realización, el dispositivo comprende un módulo de preselección de bits, que está conectado a ciertos elementos de las anteriores realizaciones del PUF para seleccionar y calcular el valor del MPF de cada transistor accionado por tensión (2) o de cada transistor accionado por corriente (1) cuando se utiliza una arquitectura no diferencial, o cada posible combinación de pares de transistores accionados por tensión (2) o cada combinación posible de pares de transistores accionados por corriente (1) cuando se utiliza una arquitectura diferencial. Estos elementos se indican con un cuadrado de líneas discontinuas en la Figura 8 para la implementación del PUF no diferencial con transistores accionados por corriente (2) , en la Figura 9 para el PUF no diferencial con transistores accionados por tensión (1) , en la Figura 10 para el PUF diferencial con transistores accionados por corriente (2) y en la Figura 11 para el PUF diferencial con transistores accionados por tensión (1) . Como se ilustra en la Figura 12, se utiliza primero un generador de direcciones (13) para pasar iterativamente la dirección al selector de transistores (3, 4) de cada transistor accionado por tensión (2) o de cada transistor accionado por corriente (1) cuando se utiliza una arquitectura no diferencial, o las direcciones de cada posible combinación de pares de transistores accionados por tensión (2) o de cada posible combinación de pares de transistores accionados por corriente (1) cuando se utiliza una arquitectura diferencial. Al hacerlo, se selecciona el transistor o par de transistores correspondiente. A continuación, las calculadoras de MPF (calculadoras de MVF (5) para la Figura 8 y la Figura 10, o calculadoras de MCF (6) para la Figura 9 y la Figura 11) calculan el valor del MPF de cada transistor accionado por tensión (2) o cada transistor accionado por corriente (1) . Estos valores se devuelven a un módulo de preselección de bits en el que el evaluador de diferencia de MPF (14) calcula la diferencia del MPF de cada transistor con respecto a un MPF de referencia, en el caso de la implementación no diferencial, o la diferencia de los valores de MPF generados por separado para cada transistor para las calculadoras de MPF para cada posible combinación de pares de transistores, en el caso de la implementación diferencial. Los transistores o pares de transistores se ordenan entonces, según los valores de diferencia MPF, por un módulo de ordenación MPF (15) . Los transistores o pares de transistores con valores de diferencia MPF más altos son seleccionados por un módulo selector (16) como aquellos que satisfacen el conjunto de criterios para la aplicación de los retos PUF. Sus direcciones se almacenan entonces en un circuito de almacenamiento (17) , desde donde se puede acceder a ellas por el generador de retos. A continuación, se describe una realización que implementa los dos métodos basados en el conteo digital de la Figura 7, que pueden utilizarse para mejorar la fiabilidad de las realizaciones anteriormente descritas del PUF, incluso cuando se utiliza el método de preselección de bits. Como se ilustra en la Figura 13, un repetidor de retos (18) genera el mismo reto c N veces y los pasa iterativamente al selector de transistores (3, 4) del PUF (representado, en la Figura 13 con un cuadrado de líneas discontinuas más el comparador MPF (12) ) para obtener las N respuestas correspondientes r. Cada una de estas N respuestas obtenidas del comparador MPF (12) se pasan a un contador digital (19) . Con la salida del contador digital (19) se pueden implementar dos dispositivos. Uno que utiliza un módulo de voto mayoritario (20) , que determina la respuesta más repetida de entre las N respuestas, y otro que utiliza un selector de bits del contador (21) , que elige sólo aquellos bits de la salida del contador digital (19) que proporcionan mejor calidad a la respuesta PUF.