- Home /

- Publicaciones de patentes /

- CONTROLADOR FLYBACK Y SISTEMA DE CARGA DE BATERÍAS

Patente nacional por "CONTROLADOR FLYBACK Y SISTEMA DE CARGA DE BATERÍAS"

Este registro ha sido solicitado por

Persona física

a través del representanteISABEL CARVAJAL Y URQUIJO

Contacto

- Estado: Vigente

- País:

- España

- Fecha solicitud:

- 19/07/2022

- Número solicitud:

-

P202230661

- Número publicación:

-

ES2958838

- Fecha de concesión:

-

- Inventores:

-

Persona física

- Datos del titular:

-

Persona física

- Datos del representante:

-

Isabel Carvajal y Urquijo

- Clasificación Internacional de Patentes:

- H02M 3/335

- Clasificación Internacional de Patentes de la publicación:

- H02M 3/335

- Fecha de vencimiento:

Quiero registrar una patente

Reivindicaciones:

+ ES-2958838_A11. Un controlador flyback (10) , configurada para la regulación de una fuente de alimentación flyback (1) que incluye un transformador (T1) y un transistor (Q1) regulado por el controlador flyback (10) , caracterizado por que el controlador flyback (10) comprende: - una primera unidad central de procesado (13) y una segunda unidad central de procesado (14) , encargadas de controlar el funcionamiento del controlador flyback (10) en tiempo real; - una memoria (15) , encargada de almacenar datos en tiempo real y el programa de ejecución de las unidades centrales de procesado (13, 14) ; - un primer bloque de muestreo de corriente (17a) , encargado de medir la corriente en el primario del transformador (T1) para su procesado por la segunda unidad central de procesado (14) ; - un bloque de muestreo de tensión de entrada (18) , encargado de la lectura y adaptación del voltaje de entrada en el primario del transformador (T1) para su procesado por la segunda unidad central de procesado (14) ; - un bloque de muestreo de tensión de salida (19) , encargado de la lectura y adaptación del voltaje de salida en el secundario del transformador (T1) para su procesado por la segunda unidad central de procesado (14) ; - un bloque de muestreo de temperatura (20) , encargado de la lectura y adaptación de la temperatura del transformador (T1) para su procesado por la segunda unidad central de procesado (14) ; - un bloque de modulación por ancho de pulsos (21) , encargado de la sincronización y control de moduladores de ancho de pulso a partir de un voltaje objetivo; - un bloque de control de tensión del transformador (22) , encargado de controlar el voltaje en el primario del transformador (T1) para evitar la saturación del primario de transformador (T1) o del transistor (Q1) ; y - una unidad de comunicación (23) , encargada de comunicar la primera unidad central de procesado (13) con una unidad de procesado maestro (50) externa para recibir unos comandos de control. 2. El controlador flyback según la reivindicación 1, caracterizado por que está configurado ara el control de la tensión de un actuador piezoeléctrico (2) . 3. El controlador flyback según la reivindicación 1, caracterizado por que está configurado para el control de la carga de una batería (9) mediante su conexión en paralelo con al menos un controlador flyback adicional (10b) . 4. El controlador flyback según la reivindicación 3, caracterizado por que comprende una unidad de sincronización (6) encargada de la sincronización, en fase o desfase, con el al menos un controlador flyback adicional (10b) mediante el uso de una señal de sincronización (SYNCIN) . 5. El controlador flyback según la reivindicación 3 o 4, caracterizado por que comprende un segundo bloque de muestreo de corriente (17b) , encargado de monitorizar la corriente de carga en el secundario del transformador (T1) , a partir de las mediciones de un sensor de efecto Hall (4) , para su procesado por la segunda unidad central de procesado (14) . 6. El controlador flyback según la reivindicación 5, caracterizado por que la segunda unidad central de procesado (14) está configurada para controlar la corriente en el primario y en el secundario del transformador (T1) mediante la activación de interrupciones cuando se sobrepasa un límite de corriente (IPRI_LIMIT, ISEC_LIMIT) programado. 7. Un sistema de carga de baterías (8) , caracterizado por que comprende una pluralidad de controladores flyback (10a, 10b; 10c, 10d) según la reivindicación 1. 8. El sistema de carga de baterías según la reivindicación 7, caracterizado por que comprende: - una pluralidad de fuentes de alimentación flyback (1a, 1b) conectadas en paralelo alimentando una batería (9) , donde cada fuente de alimentación flyback (1a, 1b) comprende un controlador flyback (10a, 10b) según la reivindicación 1, y donde cada controlador flyback (10a, 10b) comprende una unidad de sincronización (6) encargada de la sincronización, en fase o desfase, entre los controladores flyback (10a, 10b) mediante el uso de una señal de sincronización (SYNCIN) ; y - una unidad de procesado maestro (50) encargada del control de la carga de la batería (9) mediante el envío de unos comandos de control a la unidad de comunicación (23) de los controladores flyback (10a, 10b) . 9. El sistema de carga de baterías según la reivindicación 8, donde los controladores flyback (10a, 10b) de las fuentes de alimentación flyback (1a, 1b) comprenden un segundo bloque de muestreo de corriente (17b) , encargado de monitorizar la corriente de carga en el secundario del transformador (T1) a partir de las mediciones de un sensor de efecto Hall (4) . 10. El sistema de carga de baterías según la reivindicación 7, caracterizado por que comprende: - un primer controlador flyback (10c) conectado al primario del transformador (T1) y con un bloque de muestreo de tensión de entrada (18) para la lectura del voltaje de entrada en el primario del transformador (T1) ; - un segundo controlador flyback (10d) conectado al secundario del transformador (T1) y con un bloque de muestreo de tensión de salida (19) para la lectura del voltaje de salida en el secundario del transformador (T1) ; - unas unidades de procesado maestro (50c, 50d) conectadas a las respectivas unidades de comunicación (23) de los controladores flyback (10c, 10d) y encargadas del control de la carga de la batería (9) mediante el envío de unos comandos de control a los controladores flyback (10c, 10d) ; y donde cada controlador flyback (10c, 10d) comprende una unidad de sincronización (6) encargada de la sincronización entre los controladores flyback (10c, 10d) mediante el uso de unas señales de sincronización (SYNCIN, SYNCOUT) .

Los productos y servicios protegidos por este registro son:

H02M 3/335

Descripciones:

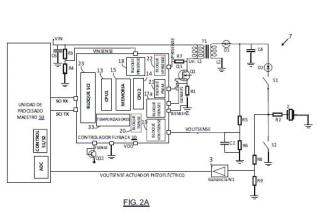

+ ES-2958838_A1 CONTROLADOR FLYBACK Y SISTEMA DE CARGA DE BATERÍAS Campo de la invención La presente invención se engloba dentro del campo de semiconductores y arquitectura de hardware para controladores flyback con aplicaciones en sistemas de carga de baterías, condensadores o supercondensadores y en sistemas de balance de células o baterías, entre otras aplicaciones. Antecedentes de la invención En la actualidad, existen numerosos controladores analógicos para regular la tensión y/o corriente de salida. Estos controladores funcionan en diferentes rangos de tensión de entrada y salida, y están gobernados por una o ninguna unidad central de proceso (CPU) . Los productos que actualmente existen en el mercado se pueden clasificar en dos grupos en función de su arquitectura de hardware: - Arquitectura analógica: Esta arquitectura se caracteriza por el uso de componentes simples con mínima capacidad de programación. Este tipo de diseños buscan la minimización del diseño de software y basan su configuración en el uso de resistencias y el control de corrientes de fuga. - Arquitectura digital: Este tipo de arquitectura se caracteriza por el uso principalmente de microcontroladores. El diseño de este tipo de arquitecturas requiere la división del diseño entre software y hardware. Esta división hace que la fase de creación de un producto final sea más cara en tiempos y complejidad ya que todas las piezas funcionales se han de unir en la fase final de producción. Sin embargo, los controladores actuales tienen una limitación tecnológica en cuanto a su adaptabilidad a aplicaciones como sistemas de radio frecuencia de programación de voltaje de pico, sistemas y circuitos desfibriladores de alta potencia, sistemas de carga y balance de baterías y sistemas de carga solar para aplicaciones aisladas. Aunque la topología flyback es ampliamente utilizada, su aplicación en sistemas de carga requiere variaciones importantes de diseño, ya que la fase de carga se podría extender urante horas. Debido a ello factores como la frecuencia de conmutación, la temperatura, la corriente o el estado integral del sistema se han de monitorizar de manera muy precisa. Estas características funcionales crean la necesidad del diseño de una arquitectura específica para un controlador flyback que permita optimizar el producto final, lo que constituye el objetivo de la presente invención. La propuesta de la presente invención establece la unión de una arquitectura analógica y una arquitectura digital con una alta optimización, seleccionando los elementos mínimos necesarios para maximizar recursos, espacio de diseño, rendimiento y costes. Descripción de la invención La presente invención se refiere a una arquitectura mixta específica y adaptable para controladores flyback, y un sistema de carga de baterías que utiliza dichos controladores flyback. La arquitectura de hardware de los controladores flyback está formada por bloques analógicos y digitales para una topología flyback especializada en sistema de carga de alto voltaje como baterías, condensadores o supercondesadores, con posibilidad bidireccional, cuya configuración se describe a continuación. La invención propuesta emplea grupos de bloques y componentes necesarios para la creación de un controlador flyback especializado en sistemas de carga con un rango programable e ideado para su integración en un único circuito integrado (tecnología SOC, System on Chip) . Un primer aspecto de la presente invención se refiere a un controlador flyback para la regulación de una fuente de alimentación flyback que incluye un transformador y un transistor regulado por el controlador flyback. El controlador flyback comprende los siguientes bloques o elementos: - Una primera unidad central de procesado y una segunda unidad central de procesado, encargadas de controlar el funcionamiento del controlador flyback (10) en tiempo real. - Una memoria, encargada de almacenar datos en tiempo real y el programa de ejecución de las unidades centrales de procesado. - Un primer bloque de muestreo de corriente, encargado de medir la corriente en el primario del transformador para su procesado por la segunda unidad central de procesado. - Un bloque de muestreo de tensión de entrada, encargado de la lectura y adaptación del voltaje de entrada en el primario del transformador para su procesado por la segunda unidad central de procesado. - Un bloque de muestreo de tensión de salida, encargado de la lectura y adaptación del voltaje de salida en el secundario del transformador para su procesado por la segunda unidad central de procesado. - Un bloque de muestreo de temperatura, encargado de la lectura y adaptación de la temperatura del transformador para su procesado por la segunda unidad central de procesado. - Un bloque de modulación por ancho de pulsos, encargado de la sincronización y control de moduladores de ancho de pulso a partir de un voltaje objetivo. - Un bloque de control de tensión del transformador, encargado de controlar el voltaje en el primario del transformador para evitar la saturación del primario de transformador o del transistor. - Una unidad de comunicación, encargada de comunicar la primera unidad central de procesado con una unidad de procesado maestro externa para recibir unos comandos de control. De acuerdo a una primera aplicación, el controlador flyback se emplea para el control de la tensión de un actuador piezoeléctrico. En otra aplicación, el controlador flyback se utilizar para gestionar la carga de una batería, preferentemente mediante su conexión en paralelo con al menos uno o varios controladores flyback adicionales. En este caso el controlador flyback comprende preferentemente una unidad de sincronización encargada de la sincronización, en fase o desfase, con los controladores flyback adicionales mediante el uso de una señal de sincronización. El controlador flyback puede comprender un segundo bloque de muestreo de corriente, encargado de monitorizar la corriente de carga en el secundario del transformador, a partir de las mediciones de un sensor de efecto Hall, para su procesado por la segunda unidad central de procesado. La segunda unidad central de procesado está preferentemente configurada para controlar la corriente en el primario y/o en el secundario del transformador mediante la activación de interrupciones cuando se sobrepasa un límite de corriente programado. Un segundo aspecto de la presente invención se refiere a un sistema de carga de baterías que comprende una pluralidad de controladores flyback descritos anteriormente. En una realización, el sistema de carga de baterías comprende: - Una pluralidad de fuentes de alimentación flyback conectadas en paralelo alimentando una batería, donde cada fuente de alimentación flyback comprende un controlador flyback, y donde cada controlador flyback comprende una unidad de sincronización encargada de la sincronización, en fase o desfase, entre los controladores flyback mediante el uso de una señal de sincronización. - Una unidad de procesado maestro encargada del control de la carga de la batería mediante el envío de unos comandos de control a la unidad de comunicación de los controladores flyback. En otra realización el sistema de carga de baterías comprende: - Un primer y un segundo controlador flyback que comprenden una unidad de sincronización encargada de la sincronización entre los controladores flyback mediante el uso de unas señales de sincronización. El primer controlador flyback está conectado al primario del transformador y dispone de un bloque de muestreo de tensión de entrada para la lectura del voltaje de entrada en el primario del transformador. El segundo controlador flyback está conectado al secundario del transformador e incluye un bloque de muestreo de tensión de salida para la lectura del voltaje de salida en el secundario del transformador. - Unas unidades de procesado maestro conectadas a las respectivas unidades de comunicación de los controladores flyback, donde las unidades de procesado maestro están encargadas del control de la carga de la batería mediante el envío de unos comandos de control a los controladores flyback. El controlador flyback de la presente invención aporta, entre otras, las siguientes ventajas: • Posibilidad de programación y configuración en fase de producción. • Rangos de aplicación de 1.- 1000 Voltios. • Posibilidad de calibración para solventar variación de procesos en caso de un semiconductor. • Rangos de corriente de 1 -50 amperios. • Rango de conmutación de 500khz a 100Hz. • Control de los estados T1, T2 y T3 en modo de conducción discontinuo (DCM) . • Control de transitorios provenientes de la fuente de alimentación (V in) . • Buena respuesta en régimen transitorio. • Control y monitorización ante la saturación del transformador flyback. • Programación en tiempo real y capacidad de monitorización sobre: • Voltaje de entrada. • Voltaje de salida. • Rangos de corriente. • Rangos de temperatura. • Variación de hardware: transformador, resistencias de muestreo o precisión de reguladores. • Control contra sobre corrientes: • En el primario del transformador, determinado por el modo de control. • En el secundario del transformador, durante la fase de descarga. • Multi-configuración sin variar el hardware en: • Regulador bidireccional. • Regulador unidireccional de conmutación simple o doble. • Posibilidad de sincronización en fase, en desfase y en modo árbol. La invención tiene, entre otras, las siguientes aplicaciones industriales: sistemas de carga de alto voltaje (condensadores, baterías o supercondensadores) y sistemas de balance (células o paquetes de baterías) . La presente invención resuelve los siguientes problemas técnicos del estado del arte a nivel electrónico: - Control y programación de los ciclos (T1, T2 y T3) en modo DCM (modo de conducción discontinuo) , e incluye la posibilidad de cambio de modo CCM (modo de conducción continuo) a DCM dependiendo del estado del sistema y la interpretación del mismo por el controlador. - Control y programación para diferentes selecciones de componentes de los límites e corriente de los estados de conducción T1, T2 y T3. - Detección de fallos para tiempos largos de carga en los estados T2 y T3, mediante el uso de CPUs e interrupciones de reloj. Estas interrupciones son programables, y por ello fácilmente adaptables a diferente sistema de carga o entornos. - Mejora de la latencia de detección de interrupciones y control de los pines PWM1 /2 de modulación de pulso con respecto a las órdenes de las unidades de control. - Mejora funcional ante interferencias provenientes de buses de comunicación en el sistema de control, mediante el aislamiento de buses mediante la memoria RAM. - Control de la corriente en el primario y secundario con el uso de interrupciones, cuya respuesta es programable dependiendo del entorno o configuración. Dicha configuración de los DACs se adapta ciclo a ciclo dependiendo del voltaje de salida. El valor máximo o mínimo es configurable a partir de la CPU asignada. - Arquitectura multipropósito programable sin necesidad de usar sistemas como RTOS (sistema operativo en tiempo real) . - Posibilidad de control de los modos de conducción y funcionamiento a partir de la temperatura en el controlador. - Control de la precisión del sistema de carga y adaptabilidad ante perturbaciones en el voltaje de entrada, configuración en tiempo real y fallo de la batería. Esto se realiza a partir del muestreo de dichas señales. - Sincronización de varios controladores a partir de señales de reloj, para incrementar los rangos de corriente. Funcionamiento en modos síncrono, asíncrono o árbol, solo durante la fase carga, para disminuir tiempos de funcionamiento. Este modo se configura con un comando digital. - Arquitectura de memoria específica para maximizar recursos de hardware y costes de diseño. A nivel de producto, la presente invención resuelve los siguientes problemas del estado del arte: - Simplificación de la fase de manufactura de productos de carga de baterías, mediante la maximización de recursos de memoria y su partición especializada. - Posibilidad de configuración de múltiples rangos de aplicación y entornos, mediante multiplexores. Esto permite reducir el uso de otros componentes pasivos activos. La presente invención permite de manera ventajosa: - Flexibilidad de programación y configuración a múltiples rangos. - Flexibilidad de programación y configuración en modo unidireccional o bidireccional por bloques simétricos e idénticos en VINSENSE y VOUTSENSE, en la arquitectura y aplicación propuesta. - Capacidad de calibración de los bloques ISENSE, VINSENSE, VOUTSENSE, VPRI cuando el hardware afecta en la precisión, mediante los convertidores digital a analógico (DACs) de cada bloque. Permite minimizar el impacto de diseño y solventar variaciones debidas a los procesos de manufactura (en otro caso habría que cambiar resistencias, cuya precisión es difícil de encontrar) . - Reconfiguración digital para voltajes y corrientes, para una configuración amplia, solo con comandos digitales. En otro caso habría que desoldar componentes y volver a verificar el sistema. - Minimización del diseño de firmware y complejidad en el diseño de productos finales para la aplicación flyback. La invención abarca la arquitectura y el sistema de control de un sistema de carga (de baterías o de condensadores) consistente en un convertidor flyback diseñado para ser controlado mediante un sistema mixto analógico/digital, es decir, incorporando bloques digitales y analógicos. La presente invención se diferencia de los convertidores del estado del arte por la unión de los siguientes tipos de bloques: • ADC: Convertidor analógico a digital. • DAC: Convertidor digital a analógico. • AO: Amplificadores operacionales. • CPU: Unidad central de proceso. • Memorias. • PLLs: Lazos de seguimiento de fase. • Reguladores de voltajes. Breve descripción de los dibujos A continuación, se pasa a describir de manera muy breve una serie de dibujos que ayudan a comprender mejor la invención y que se relacionan expresamente con una realización de dicha invención que se presenta como un ejemplo no limitativo de ésta. La Figura 1 representa un esquema de una fuente de alimentación flyback típica. La Figura 2A muestra un diagrama esquemático de un controlador flyback de acuerdo a una realización de la presente invención. La Figura 2B muestra las señales a controlar mediante el controlador flyback de la realización de la Figura 2A. La Figura 2C muestra la sincronización de dos controladores flyback en paralelo aplicado a un sistema de carga. La Figura 2D muestra las señales de tensión (V1, V2) y tiempos (T1, T2) a controlar en la realización de la Figura 2C. La Figura 2E muestra las señales a controlar mediante la realización de la Figura 2C para las señales SINCIN en sincronización en desfase. La Figura 2F muestra las señales a controlar mediante la realización de la Figura 2E para las señales SINCIN en sincronización en fase. La Figura 2G muestra un modo de control doble y de sincronización de dos controladores flyback de conmutación doble. La Figura 2H muestra las señales utilizadas en la sincronización de dos controladores flyback de conmutación doble. La Figura 3 ilustra la arquitectura hardware de un controlador flyback de acuerdo a una realización de la presente invención. La Figura 4 muestra una realización de la división de relojes de las dos CPUs. La Figura 5 muestra una arquitectura de memoria propuesta para las dos CPUs de acuerdo a una realización. La Figura 6 describe el bloque analógico ADC de acuerdo a una posible realización. La Figura 7 muestra el proceso de conversión de señales analógicas a digitales por parte del bloque ADC. La Figura 8 ilustra una realización del bloque analógico TSENSE, que recibe una señal de un sensor de temperatura. La Figura 9 muestra el funcionamiento del bloque TSENSE. La Figura 10 ilustra una realización del bloque analógico VPRI. La Figura 11 muestra el funcionamiento del bloque VPRI. La Figura 12 representa la jerarquía de buses y bloques de la arquitectura propuesta según una realización. La Figura 13A ilustra una realización del bloque analógico ISENSE (el mismo bloque representado en la figura para ISENSE1 y ISENSE2) . La Figura 13B ilustra el funcionamiento de los bloques ISENSE1 y ISENSE2 en relación a aplicaciones con alto ruidos y transitorios debidos a la conducción de Q1. La Figura 14 representa una realización del bloque analógico DAC. La Figura 15 ilustra el funcionamiento del controlador en modo DCM. La Figura 16 describe el funcionamiento del controlador en modo CCM. La Figura 17 representa una realización del bloque analógico VOUTSENSE. El mismo esquema corresponde al bloque analógico VINSENSE. La Figura 18 describe el bloque digital PWM. La Figura 19 describe el funcionamiento propuesto de la ejecución de interrupciones CPU2. La Figura 20 ilustra el funcionamiento y descripción de las fases de carga. La Figura 21 ilustra un diagrama de flujo del algoritmo de control de acuerdo a una realización. La Figura 22 ilustra un diagrama de flujo del algoritmo de programación de acuerdo a una realización. La Figura 23 muestra un diagrama de flujo del algoritmo de protección de acuerdo a una realización. La Figura 24 describe el bloque digital GPIO/PWM. Las Figuras 25A y 25B describen el modo de sincronización de acuerdo a una realización. La Figura 26 ilustra el funcionamiento del sistema de sincronización. La Figura 27 muestra una aplicación de la presente invención en radio frecuencia y un sistema de desfibrilador. La Figura 28 ilustra una aplicación de la presente invención en sistemas de balance de baterías. La Figura 29 muestra una aplicación de la presente invención en un sistema bidireccional. La Figura 30 muestra una aplicación de la presente invención en un sistema de aprovechamiento de energía solar. Descripción detallada de la invención La Figura 1 muestra un esquema básico de una fuente de alimentación flyback 1 típica, la cual es una fuente de alimentación regulada con topología tipo flyback de alta potencia regulada por voltaje o corriente, que permite ajustar voltajes en un determinado rango de tensión y es capaz de proporcionar un voltaje programable. La fuente de alimentación flyback 1 comprende un controlador o regulador principal (controlador flyback 10) , un transformador T1, un transistor Q1, y un conjunto de resistencias (R1, R3, R4, R5, R6) y condensadores (C1, C3) . La fuente de alimentación flyback 1 opera como un cargador de baterías, con muestreo de corriente en el primario (I_SENSE) , muestreo del voltaje de salida (VOUT_SENSE) y, opcionalmente, muestreo del voltaje de entrada (VIN_SENSE) . El muestreo de estos voltajes y corrientes se efectúa mediante la división de voltajes para evitar el dañado del controlador flyback 10. El voltaje VIN_SENSE está dividido mediante las resistencias R3 y R4, el voltaje VOUT_SENSE está divido mediante las resistencias R5 y R6, y el cálculo de la corriente I_SENSE se determina mediante el muestreo el voltaje en la resistencia R1. El uso de esta topología permite la miniaturización de la arquitectura de hardware y su simplificación. La fuente de alimentación flyback 1 es programable en rangos de voltaje y corriente. La programación de dicho voltaje se realiza mediante el control del ciclo de trabajo del transistor Q1 por parte del controlador flyback 10. Como caso general el voltaje de salida de una topología flyback se rige por la siguiente relación (donde N es la relación de bobinado del transformador T1, D es el ciclo de trabajo del transistor Q1, V in es la tensión o voltaje de entrada de la fuente de alimentación flyback 1, VOUT es la tensión o voltaje de salida de la fuente de alimentación flyback 1) : La Figura 2A muestra un diagrama esquemático de un sistema de control 7 de un actuador piezoeléctrico 2 utilizando un controlador flyback 10 de acuerdo a una realización de la presente invención. Estos sistemas, conocidos como "piezomotiorí, se caracterizan por poseer múltiples rangos de voltajes que pueden oscilar entre unos pocos voltios hasta 1000 V, ya que al ser actuadores capacitivos su capacidad de extensión, activación o fuerza depende del voltaje utilizado. El ejemplo de la Figura 2A muestra un circuito de control para un actuador de voltaje positivo. Este voltaje y control permite el control sobre las variables detalladas en la gráfica de la Figura 2B. El tiempo de subida o bajada, determinados por T1 y T2 en las gráficas de la Figura 2B, depende de la resistencia R2. El muestreo del voltaje presente en el elemento piezoeléctrico a través de un amplificador 3 permite la readaptación del rango de voltaje a partir de los comandos de una unidad de procesado maestro 50. Los bloques requeridos que incluye el controlador flyback 10 para un control eficaz del voltaje de salida son los siguientes (además de los bloques de generación de relojes y regulación necesarios para su funcionamiento) : - Primera unidad central de procesado 13 (CPU1) y segunda unidad central de procesado 14 (CPU2) : encargadas de controlar el funcionamiento del controlador flyback 10 en tiempo real, a partir de un software alojado en una memoria 15 - Memoria 15: encargada de almacenar datos en tiempo real y el programa de ejecución de las CPUs (13, 14) . - Bloque de muestreo de corriente 17a (ISENSE1) : encargado del sensado de corriente en el primario del transformador T1 para su posterior procesado por la segunda CPU 14 (CPU2) . - Bloque de muestreo de tensión de entrada 18 (VINSENSE) : encargado de la lectura y adaptación del voltaje de entrada en el primario del transformador T 1 para su posterior procesado por la segunda CPU 14 (CPU2) . - Bloque de muestreo de tensión de salida 19 (VOUTSENSE) : encargado de la lectura y adaptación del voltaje de salida en el secundario del transformador T1, para su posterior procesado por la segunda CPU 14. - Bloque de muestreo de temperatura 20 (TSENSE) : encargado de la lectura y adaptación de la temperatura del transformador T1 para su posterior procesado por la segunda CPU 14. - Bloque PWM 21 (modulación por ancho de pulsos) : encargado de la sincronización y control de moduladores de ancho de pulso, a partir del voltaje objetivo del sistema. - Bloque de control de tensión del transformador 22 (VPRISENSE) : encargado del control del voltaje en el primario de transformador T1 para evitar la saturación del primario de transformador T1 o del transistor Q1; - Unidad de comunicación 23 (bloque SCI) : encargada de la comunicación y transmisión del funcionamiento en tiempo real del sistema, comunicando la primera unidad central de procesado 13 con la unidad de procesado maestro (50) externa, para que la unidad central de procesado 13 pueda recibir unos comandos de control procedentes de la unidad de procesado maestro (50) . - Temporizadores 33, usados por las CPUs (13, 14) . La ilustración mostrada en la Figura 2A se considera ideal para baja potencia. Para altas potencias, la lectura de los voltajes está subyugada a la necesidad de un sistema de aislamiento galvánico, mediante el uso de un opto-acoplador o un amplificador diferencial con aislamiento galvánico en el lectura del voltaje VOUTSENSE. La Figura 2C muestra, de acuerdo a una realización de la presente invención, un diagrama esquemático de un sistema de carga de baterías 8 utilizando una pluralidad de controladores flyback conectados en paralelo. En particular, la Figura 2C muestra la sincronización de dos controladores flyback (10a, 10b) en paralelo (aunque se pueden conectar más controladores flyback en paralelo) aplicado para cargar una batería 9 o lemento de almacenamiento de alta absorción de corriente. La sincronización de dos o más controladores flyback en paralelo permite la generación de pulsos de corriente, los cuales dependiendo de si su sincronización es en fase, desfase o árbol, puede multiplicar la corriente por tantos controladores en paralelo cuando están sincronizados en fase (Figura 2F hasta crear un sistema de carga continuo mitigando las pérdidas de tiempo durante el estado de conducción del transistor Q1. Si la sincronización está desfasada (Figura 2E se mitiga las pérdidas de tiempo de Q1. Durante la carga de la batería 9 se suponen que existen altos rangos de corriente; por ello, la monitorización de la corriente de carga, aunque no es obligatoria, sí es recomendable. La monitorización de la corriente de carga se ha representado en la Figura F2C a partir de un sensor de efecto Hall 4, cuya adaptación se realiza mediante un amplificador diferencial 5 para el procesado a partir de la segunda CPU 14 (CPU2) y un segundo bloque de muestreo de corriente 17b (ISENSE2) que tiene la función de leer y acomodar las corrientes capturadas en el secundario del transformador T 1. De manera ventajosa, el sistema de carga de baterías 8 de la Figura 2C permite la reducción de los tiempos de carga mediante la sincronización de los controladores flyback (10a, 10b) con el uso de una señal de sincronización (SYNCIN) . Dicha señal tiene un efecto sobre la señal del modulador de ancho de pulso que actúa sobre el transistor Q1, después de su procesado por la segunda CPU 14 (CPU2) . Otra ventaja adicional es la monitorización simple de la corriente en el secundario del transformador T1 sin necesidad de aislamiento galvánico mediante el uso de un sensor de efecto Hall 4. Como se muestra en la Figura 2D, este circuito solo tiene control sobre los voltajes V1, V2 y los tiempos T1 o T2. La lectura del voltaje objetivo puede ser procesada por alguno de los controladores flyback (10a, 10b) de la Figura 2C. La unidad de procesado maestro 50 tiene el control sobre el estado de carga, activación o desactivación de la sincronización a partir del bloque SCI 23 y su procesado por la primera CPU 13 (CPU1) . La sincronización de los distintos controladores flyback (10a, 10b) en paralelo se realiza mediante una señal digital de sincronización (SYNCIN) que, en su activación en flanco de subida, activa la señal PWM1 del modulador de ancho de pulso que actúa sobre el transistor Q1, de forma que en el modo de sincronización en fase se incrementan los rangos de corriente plicados a la carga, y en el modo de sincronización en desfase existe un retraso para crear una carga continua de corriente. Los bloques requeridos en los controladores flyback para un control eficaz del sistema de carga de baterías 8 representado en la Figura 2C son los siguientes (además de los bloques de generación de relojes y regulación necesarios para su funcionamiento) : - Primera CPU 13 (CPU1) y segunda CPU 14 (CPU2) . - Memoria 15. - Bloques de muestreo de corriente 17a (ISENSE1) y 17b (ISENSE2) . - Bloque de muestreo de tensión de entrada 18 (VINSENSE) . - Bloque de muestreo de tensión de salida 19 (VOUTSENSE) . - Bloque de muestreo de temperatura 20 (TSENSE) . - Bloque PWM 21. - Bloque de control de tensión del transformador 22 (VPRISENSE) . - Bloque SCI 23. - Temporizadores 33. - Bloque o unidad de sincronización SYNC 6, encargada de la sincronización entre los controladores flyback mediante el uso de una señal de sincronización (SYNCIN) . La Figura 2G muestra un diagrama esquemático de otra realización de un sistema de carga de baterías 8 utilizando una pluralidad de controladores flyback. De acuerdo a esta realización, se realiza un modo de control doble y de sincronización de dos controladores flyback de conmutación doble (un primer controlador flyback 10c conectado al primario del transformador T1 y un segundo controlador flyback 10d conectado al secundario del transformador T1) . Este control y sincronización se realiza mediante el uso de las señales SYNCIN y SYNCOUT, como se muestra en la Figura 2H, con el objetivo de sincronizar los modos de control de los controladores desde el primario y el secundario. Esta realización tiene como objetivo mitigar la integración y programabilidad en la fase de fabricación de los controladores flyback o módulos de potencia para múltiples rangos en sistemas de carga o balance de baterías, ya que dependiendo de si la batería 9 está dividida en paquetes con múltiples células los rangos e voltaje pueden variar, requiriendo además, en algunos casos, el modo de control bidireccional. Los bloques mínimos requeridos para un control eficaz del voltaje de salida son: primera CPU 13 (CPU1) , segunda CPU 14 (CPU2) , memoria 15, bloque de muestreo de corriente 17a (ISENSE1) , bloque de muestreo de tensión de entrada 18 (VINSENSE) en el primer controlador flyback 10c, bloque de muestreo de tensión de salida 19 (VOUTSENSE) en el segundo controlador flyback 10d, bloque de muestreo de temperatura 20 (TSENSE) , bloque PWM 21, bloque VPRISENSE 22, bloque SCI 23, temporizadores 33, bloque SYNC 6, además de los bloques de generación de relojes y regulación necesarios para su funcionamiento. La Figura 3 ilustra un diagrama de bloques de la arquitectura de hardware de un controlador flyback 10 de acuerdo a una realización. El controlador flyback 10 representado en el ejemplo de la figura se emplea dentro un sistema de alimentación (fuente de alimentación flyback 1) para cargar una batería 9 o condensador e incluye los siguientes bloques funcionales: - Oscilador interno 11: bloque funcional encargado de general la señal de reloj para todos los bloques digitales, como las CPUs (unidades centrales de procesado) , memoria o buses de comunicación. - PLL 12 (lazo de seguimiento de fase) : Bloque encargado de multiplicar la señal de referencia proveniente del oscilador y dividirla entre los siguientes bloques funcionales como CPUs, ADCs (convertidores analógico a digital) , memoria, buses de comunicaron, tal y como se representa en la Figura 4 , la cual muestra la división de relojes CPU1/CPU2 de acuerdo a una posible realización de la arquitectura propuesta. - CPUs (13, 14) : Unidades centrales de procesado que comprenden una primera CPU 13 (CPU1) y una segunda CPU 14 (CPU2) encargadas de controlar el funcionamiento del controlador flyback 10 en tiempo real, a partir de un software alojado en una memoria 15. - Memoria 15: Bloque funcional encargado de almacenar datos en tiempo real y el programa de ejecución de las CPUs (13, 14) . Puede incluir, por ejemplo, una memoria ROM 15a, una memoria OTP 15b (programable una sola vez) , una memoria flash 15c, una memoria RAM compartida 15d entre la CPU1 y la CPU2, y una memoria SRAM CPU1 15e (para la CPU1) y una memoria SRAM CPU2 15f (para la CPU2) . La Figura 5 muestra la división y arquitectura de memoria mínima propuesta CPU1/CPU2 de acuerdo a una realización, incluyendo un banco de registros CPU1 15g, un banco de registros CPU2 15h, una tabla de vectores CPU1 15i, una tabla de vectores CPU2 15j y unos parámetros de configuración 15k incluidos en la memoria flash 15c. A continuación, se describe cada elemento: • Memoria ROM 15a: Almacenamiento de un cargador de arranque (o bootloader) . Este software tiene la función de activar el programa en sus funciones básicas. En caso de fallo de memoria, el cargador de arranque siempre tendría capacidad de control y lectura sobre todas las regiones de memoria. • Banco de registros (15g, 15h) : Región de memoria que posee los registros de configuración de cada uno de los bloques anexos. • Tabla de vectores (15i, 15j) : Región de memoria que contiene el control de las interrupciones y las direcciones de arranque en la memoria RAM. • Memoria compartida CPU1/CPU2 15d: Memoria de intercambio que tiene la función de compartir datos y variables entre la CPU1 y CPU2 en tiempo real. En esta región se programan valores de protección, voltajes y corriente objetivo. • Memoria SRAM (15e, 15f) : Memoria de ejecución usada durante la ejecución de los firmwares donde se almacenan, en el periodo normal de ejecución CPU1/CPU2, tabla de vectores (interrupciones) y valores de registros de escritura y lectura de cada bloque funcional. Cada CPU tiene asignada una dirección de comienzo y final para su lectura. • Memoria flash 15c: Memoria empleada para el almacenamiento de los firmwares, tanto para la CPU1 como la CPU2. Este software tiene la capacidad final funcional del sistema de carga de baterías. Cada CPU tiene asignada una dirección de comienzo y final para su lectura. La copia de datos de la memoria flash a RAM se realiza exclusivamente por la CPU1. En esta región se programan unos parámetros de configuración 15k incluyendo valores de protección, calibración, voltajes y corriente objetivo, en la dirección predeterminada. • Memoria OTP: Memoria con la función de almacenar datos de manufactura, como son fecha, localización y operador. Acceso limitado solo desde la CPU1. - Bloque ADC 16 (convertidor analógico a digital) : El bloque ADC 16 tiene la función de leer las variables analógicas y conmutar los multiplexores para su procesado por la CPUs (13, 14) . El bloque ADC 16 puede leer o muestrear los valores de tensión de entrada VINSENSE, tensión de salida VOUTSENSE y temperatura del transformador TSENSE a partir del control de un multiplexor 27 (mediante la señal reg_mux_adc_ctrl, tal y como se muestra en la Figura 6 que describe el bloque ADC 16 de acuerdo a una posible realización) . La Figura 7 muestra el proceso de conversión de señales analógicas a digitales: Mediante la activación en la segunda CPU 14 (CPU2) de uno de sus temporizadores 33 y su configuración en una frecuencia determinada, se genera una señal de reloj estable, la cual genera una interrupción de tiempo en la CPU2. Esta activación de la interrupción permite que la CPU2 salte sobre una región de memoria SRAM (Figura 5) , en la cual mediante el control de la señal de multiplexor reg_mux_adc_ctrl (Figura 6) , permite la lectura de las señales provenientes de los pines VOUTSENSE (vout_diff_sense) , VINSENSE (vin_diff_sense) , TSENSE (Temp_diff_sense) o ADJ (adj_sense) . Esta señal puede controlarse para que cada una de las lecturas sea x1, x2 o xn hasta el límite del temporizador. - Bloques de muestreo de corriente ISENSE (17a, 17b) : Bloques de sensado de corriente que tienen la función de leer y acomodar las corrientes capturadas en el primario (primer bloque de muestreo de corriente 17a, ISENSE1) y secundario (segundo bloque de muestreo de corriente 17b, ISENSE2) del transformador T1 para su posterior procesado por las CPUs (13, 14) . - Bloque de muestreo de tensión de entrada 18 (VINSENSE) : Bloque encargado de la lectura y adaptación del voltaje de entrada en el primario del transformador T1 para su posterior procesado por el ADC 16 y la segunda CPU 14 (CPU2) . - Bloque de muestreo de tensión de salida 19 (VOUTSENSE) : Bloque encargado de la lectura y adaptación del voltaje de salida en el secundario del transformador T1, para su posterior procesado por el ADC 16 y la CPU a su cargo (segunda CPU 14) . - Bloque de muestreo de temperatura 20 (TSENSE) : El bloque TSENSE 20 está encargado de la lectura y adaptación de la temperatura del transformador T 1, para su posterior procesado por el ADC 16 y la CPU a su cargo (segunda CPU 14) . La Figura 8 ilustra una realización del bloque TSENSE 20, que recibe la señal de salida de un sensor de temperatura 29. La Figura 9 muestra el funcionamiento del bloque TSENSE 20 de la Figura 8. El bloque TSENSE 20 está diseñado para captar la señal de temperatura proveniente de un componente específico, que utilicen diodos térmicos u otro de salida única. El uso del DAC2 (Figura 8) controlado a partir de la señal cpu_dac2_reg, permite la calibración de la lectura del voltaje y la adaptación de dicho voltaje a un rango que permite solucionar el error de offset del ADC. - PWM 21: Bloque encargado de la sincronización y control de los moduladores de ancho de pulso PWM1 y PWM2, a partir del voltaje objetivo del sistema. - VPRI 22: Bloque encargado del control del voltaje en el primario del transformador T1 durante la fase de carga. La Figura 10 ilustra una realización del bloque VPRI 22. La Figura 11 muestra el funcionamiento del bloque VPRI 22 de la Figura 10, donde el DAC3, el diodo D1 y las resistencias R7 y R8, permiten el control para evitar la saturación del primario de transformador o del transistor Q1. El transitorio pos conducción del transistor Q1 depende del voltaje de salida, y la energía remanente durante las fases de conducción 2 o 3 depende de los modos de conducción CCM o DCM. Este bloque permite el control de dichos transitorios para proteger el circuito mediante la programación del DAC3 dependiendo de estado de carga. Esta referencia podría utilizarse para determinar el voltaje de salida, pero solo en aplicaciones específicas. - Unidad de comunicación 23 (SCI /UART /I2C) : Bloque encargado de la comunicación y transmisión del funcionamiento en tiempo real del sistema. - GPIO (Entrada/Salida de Propósito General) 24: Bloque encargado del control de las señales digitales, tanto de entrada como de salida. Los pines involucrados son: PWM1, PWM2, PG, CHARGE, SYNCIN y SYNCOUT. - Bloque DACs (convertidores digital a analógico) : Bloque de varios convertidores digital-analógico (DACn_a, DACn_b, DACn_c) 25 encargado de ajustar los parámetros igitales como voltajes de referencia, límites de corriente, valores de calibración o límites de voltaje, en los bloques VINSENSE 18, VOUTSENSE 19, TSENSE 20, VPRI 22, ISENSE1 17a e ISENSE2 17b. Los DACs 25 permiten la calibración en fase de fabricación y compensar los errores de hardware debidos a diferentes causas. Dichos errores (VError m em) se almacenan en memoria para su posterior procesado. El valor final del DAC (VDACx) en los bloques ISENSE1 o ISENSE2 sería el valor de referencia (Vvaiue ref) más la suma o resta de error almacenado en memoria durante la fase de manufactura (VError_mem) . - Reguladores 26: La diferencia de voltaje entre los bloques analógicos (v_ana) y digitales (v_digi) hace necesario el uso de reguladores internos. Dichos reguladores, adaptan el voltaje para la correcta precisión de ADCs, DACs y control digital. Los pines de suministro están determinados por VDD y VS (Figura 3) . - Multiplexor 27: Son controlados a través de un bloque comparador 30 representado en la Figura 12, la cual ilustra la jerarquía de buses y bloques de la arquitectura propuesta de acuerdo a una posible realización. Tiene la función de controlar los DACs de los bloques ISENSE1 17a, ISENSE2 17b, VINSENSE 18, VOUTSENSE 19, TSENSE 20. El control de la carga de la batería se realiza en la segunda CPU 14 (CPU2) . La división en dos unidades centrales de procesado (CPU1 y CPU2) permite la mejora del rendimiento asignando tareas diferenciadas a cada uno, por lo que no es necesaria la implementación de un sistema operativo en tiempo real (RTOS) . La comunicación entre la CPU1 13 y la CPU2 14 se realiza mediante la región de memoria RAM compartida 15d. El control de la carga está determinado por el modo de conducción discontinuo (DCM) , con dos variaciones funcionales: 1. Carga programada: Durante el estado inicial de funcionamiento el transistor Q1 conduce hasta un límite determinado, programado por el convertidor digital a analógico DAC1 25, representado en la Figura 13A (donde se describe los bloques de muestreo de corriente ISENSE1 17a e ISENSE 2 17b y un bloque comparador 28) y en la Figura 14 (donde se representa el bloque de los convertidores digital a analógico DACs 30 que incluye una interfaz bus eriférico CPU2 31 para comunicarse con la CPU2 14, una unidad de control DACs 32 y los propios DACs 25) , y configurado a partir de un comando de comunicación IPRI_LIMIT, en la CPU1 13. La Figura 13B ilustra el funcionamiento de los bloques ISENSE1 y ISENSE2 en relación a aplicaciones con alto ruidos y transitorios debidos a la conducción de Q1, donde la interrupción es detectada antes del ruido, la ventana "Área de ruido" es el tiempo que el circuito necesita para estar en calma después de la conmutación de Q1, y la ventana de adaptación es el instante de tiempo para que el controlador pueda leer las variables de entorno del ADC o conducción del resto de elementos, siendo estos instantes son procesados por la CPU2. Cuando dicho límite IPRI_LIMIT es alcanzado, el bloque de muestreo de corriente ISENSE (Figura 15, donde se describe, para el modo de conducción discontinuo DCM, el control de los estados T1 (Q1=ON, D1=OFF) , T2 (Q1 =OFF, D1 =ON) y T3 (Q1 =OFF, D1 =OFF) , la intensidad IPRI en el primario del transformador T1 y la intensidad ISEC en el secundario del transformador T1) , ya sea por franco de subida o bajada, activa la interrupción cpu_pwm_isr_x (donde x es 1 para ISENSE1 y 2 para ISENSE2) . A partir de este estado, la CPU2 14 desactiva el transistor Q1 (pasando al estado T2, programando el estado de la configuración de Q1 en OFF) en función del voltaje de salida VOUT, programado mediante un comando VOUT_COMMANDO, a través de la CPU1 13. Dicho voltaje de salida Vout se muestrea y se acondiciona a partir del bloque VOUTSENSE 19. El error diferencial del valor de VOUT_COMMANDO y el valor leído por el bloque VOUTSENSE 19, afecta a los DAC 1 y DAC2 de los bloques ISENSE (17a, 17b) , ya que durante la fase final carga el modo de control ideal es un modo de conducción continuo CCM (Figura 16, donde se describe el control de los estados T1 (Q1=ON, D1=OFF) y T2 (Q1=OFF, D1=ON) del modo de conducción continuo CCM) para evitar el dañado de la batería 9. El bloque VOUTSENSE 19 realiza el muestreo directo o diferenciado con el valor de referencia del DAC5 controlado por el comando VOUT_COMANDO (Figura 17, que describe el bloque VOUTSENSE 19) y el control del multiplexor cpu_mux_dac1/2. Si se selecciona el valor directo, el cómputo se realizaría en el firmware de la CPU2 14. 2. Carga con control de corriente: Durante el estado inicial de funcionamiento el transistor Q1 conduce hasta un límite determinado y programado por el DAC1 (Figuras 13 y 14) en el bloque ISENSE1 17a. El valor de DAC1 es configurado a partir del comando de comunicación IPRI_LIMIT, a partir de la CPU1 13. Cuando dicho límite IPRI_LIMIT es alcanzado, el bloque ISENSE (Figura 15) ya sea por franco de subida o bajada, activa la interrupción cpu_pwm_isr. A partir de este estado, la CPU2 14 desactiva el transistor Q1 y activa el transistor Q2. Se muestrea la corriente de carga ISEC, por ello este límite se encuentra muestreado en el bloque ISENSE2 17b, a partir del DAC1 o DAC2 (Figura 13) , programado con el comando ISEC_LIMIT. El control del estado T3 del modo de conducción discontinuo DCM se realiza a partir de la interrupción cpu_pwm_d3_isr y su programación a partir del comando DCM_D3_COMMANDO. Cuando la interrupción cpu_pwm_d3_isr_x (donde x es 1 para ISENSE1 y es 2 para ISENSE2) se ha activado en la CPU2, el transistor Q2 se desactiva y el temporizador correspondiente comienza a contar hasta el límite DCM_D3_COMMANDO, ya que activa la interrupción de tiempo. Cuando la interrupción de finalización se activa, comienza el modo de conducción T1, con el estado del transistor Q1 activado. Esta operación se realiza de manera paralela; por ello, la CPU2 está a cargo de otras operaciones, como protección, o lectura del ADC. El valor de los DACs en los bloques ISENSE1 y ISENSE2 está determinado por el valor del voltaje de salida y el estado final de carga. Dichos parámetros son configurados con el comando VOUT_COMMANDO, al igual que la carga programada. Cada uno de los instantes de tiempo determinados por T3 o T2 en el modo programado se realiza con la activación de interrupciones de tiempo. Este se realiza mediante el uso de un temporizador dentro de la CPU2, como se muestra en la Figura 12. La precisión de dicho temporizador depende de las características del PLL y la CPU, así como sus frecuencias de referencia. Las latencias entre la velocidad de conmutación de los comparadores del bloque comparador 28 en los bloques ISENSE1 y ISENSE2 y la detección de la CPU, podría producir un cortocircuito; por ello, se hace necesario el uso de señales de control como se muestra en la Figura 18, que describe el bloque PWM 21. El control del pin PWM1 o PWM2 requiere el control de las señales cpu_pwm_d3_isr_x, cpu_pwm_isr y las señales de la CPU2 controladas por reg_pin_pwm1 y reg_pin_pwm2. Dichas señales pueden ser multiplexadas a partir del control del multiplexor pwm2_mux. En la Figura 19 se incluye un ejemplo de funcionamiento ropuesto para la ejecución de interrupciones (ADC_isr, cpu_pwm_isr, cpu_pwm_d3_isr) del bloque ADC 16 y PWM 21 en la CPU2. Durante toda la fase de carga el controlador realiza el muestreo de las diferentes señales como son: tensión de entrada V in (Figura 3) a partir de VINSENSE, temperatura de funcionamiento a partir del bloque de muestreo de temperatura 20 TSENSE, el estado del transformador después de la descarga a partir del bloque VPRI 22. La activación o desactivación del modo de carga se puede realizar mediante un comando OPERACIÓN determinado en una fase de configuración del sistema que se describirá más adelante, o mediante el uso del pin digital CHARGE (Figura 3) . Como se muestra en la Figura 20, la cual describe el funcionamiento de las fases de carga, el funcionamiento de la carga depende del estado del sistema de carga. El control se realiza mediante el muestreo de la tensión de salida Vout a partir de VOUTSENSE. Las fases de carga mínimas propuestas se detallan a continuación: • Fase de inicialización 40: El sistema de carga realiza un control de la carga por corriente. El sistema de carga se encuentra con un bajo voltaje objetivo, por ello durante el estado de conducción de Q1 el primario del transformador T1 se carga hasta un límite alto. Durante el segundo estado de conducción de Q2, el transformador T1 se descarga sobre la batería 9 o condensador. La fase de inicialización se establece hasta un primer límite de tensión de carga (por ejemplo, hasta un 10% del voltaje objetivo) , controlado por el estado del valor diferencial del comando VOUT_COMMANDO y el valor de VOUTSENSE. • Fase de carga 41: La fase de carga 41 se establece entre un primer límite de tensión de carga (e.g. 10% del voltaje objetivo) y un segundo límite de tensión de carga (e.g. 90% del voltaje objetivo) , con un funcionamiento similar a la fase de inicialización (carga con control de corriente) , pero con un control progresivo del comando IPRI_LIMIT y su DAC anexo. • Fase de regulación 42: El voltaje de la batería 9 está cerca de su límite determinado por el comando VOUT_COMANDO. Cuando la tensión supera el segundo límite de tensión de carga (e.g. 90%) , a partir de este estado el modo de conducción ideal es n modo de conducción continuo CCM. Por ello el control de IPRI_LIMIT y ISEC_LIMIT, y sus DACs anexos (Figuras 13 y 14) se programan para evitar la sobrecarga de la batería 9 hasta que se carga por completo y el sistema de carga desactiva. La Figura 21 representa un diagrama de flujo de un algoritmo de control de acuerdo a una realización. Cuando la carga o activación del controlador se realiza a partir del pin CHARGE o el comando OPERACIÓN, la CPU2 activa el pin PWM1 de nivel bajo a alto. Esto hace que la corriente en el primario aumente hasta el límite programado por el DAC2 mediante el comando ISENSE1A_COMMANDO. Cuando el límite se alcanza la señal cpu_pwm_isr_x pasa de nivel alto a bajo, por ello activa la interrupción relacionada en la CPU2. Esta activación hace que la CPU2 salte a la región de memoria RAM pre-programada en la tabla de vectores. Cuando esta función se activa, pone a nivel bajo el estado del pin PWM1. La CPU2 a partir del estado del comando OPERACIÓN en el bit (2) , puede determinar si se ha de utilizar únicamente el bloque ISENSE1 (carga programada) o ISENSE1 y ISENSE2 (carga regulada) . Si el modo de carga es programada, la CPU2 retorna a su posición de origen, activando en su camino el temporizador Toff, el cual controla el estado de conducción de D1; si la interrupción se activa, desactiva dicho temporizador y modifica el estado del pin PWM1, poniéndolo a nivel alto. Si el por el contrario la carga es regulada, la CPU2 activa el pin PWM2, poniéndolo a nivel alto, la CPU2 retorna a su origen hasta que la interrupción cpu_pwm_D3_isr se activa, saltando del mismo modo a otra región de memoria pre-programada en la tabla de vectores, poniendo el estado del pin PWM2 a nivel bajo. Si el modo de conducción es discontinuo, la CPU2 activará el temporizador en un instante de tiempo predeterminado para el estado T3 del modo de conducción discontinuo. Una vez que el T3 se activa, después del retorno de la CPU2 a su posición de memoria de origen, activará el pin PWM1 de nuevo. El controlador flyback 10 tiene una fase de programación previa, donde se programan las CPUs, ya que la memoria inicialmente se encuentra sin firmware de ejecución para la CPU1 y CPU2. En la Figura 22 se muestra un algoritmo de programación de la CPU1 y de la CPU2, de acuerdo a una realización. El funcionamiento del controlador flyback se realiza mediante la CPU1 y un cargador de arranque (bootloader) . El cargador de arranque se encuentra en la memoria ROM 15a. La memoria ROM 15a puede programarse en producción, lo que permite la reducción de tiempos de trabajo durante la fase de manufactura del controlador flyback. El cargador de arranque programado en la memoria ROM 15a posee comandos básicos de funcionamiento, como son: Leer dirección de memoria, programar dirección de memoria, estado del controlador y ejecución de firmware. La precisión de dichos comandos está determinada por la precisión de la CPU y el marco del bus de comunicación seleccionado. A continuación, se detallan una serie de comandos mínimos propuestos en el cargador de arranque: - BOOTLOADER_VERSION: Lectura de la versión de bootloader. - REG_ADDR_COMMANDO: Carga de la dirección de un registro especifico (lectura o escritura) . - REG_DATO_COMMANDO: Carga de los datos de un registro especifico. - FLASH_ADDR_COMMANDO: Almacenamiento de la dirección flash a leer o programar. - FLASH_DATO_COMMANDO: Dato a almacenar en la dirección flash. - FLASH_CONTROL_COMMANDO: Control de almacenamiento sobre la dirección FLASH y ejecución del firmware El estado de fase de programación no proporciona funcionabilidad alguna al controlador flyback en su fase de regulación o carga. Por ello es necesario cargar un firmware de control en la memoria flash 15c o SRAM (15e, 15f) , dependiendo de su partición entre las CPU1 y CPU2. La programación en las regiones de memoria FLASH pertinentes se lleva a cabo mediante los comandos programados del cargador de arranque. Una vez que los firmwares de la CPU1 y la CPU2 se han cargado en las regiones de memoria flash 15c mediante el bus de comunicación del controlador, la ejecución del firmware se realiza en la memoria SRAM (15e, 15f) ya que posee una mejor velocidad de ejecución. Por ello, el firmware alojado en memoria flash 15c se ha cargar en la RAM después de cada reinicio, ya que la memoria RAM solo posee almacenamiento temporal. El controlador flyback 10 tiene también una fase de configuración, en la cual se realiza la configuración del sistema mediante la comunicación de comandos para su posterior almacenamiento en la memoria. La precisión (tamaño) de los comandos se puede establecer entre 8 y 32 bits, dependiendo de la precisión de la CPU seleccionada. A continuación, se describen una serie de comandos propuestos a modo de ejemplo: - OPERACIÓN: Comando de control digital del controlador, permitiendo inicio/parado de carga, configuración maestro en modo de sincronización y configuración esclavo en modo de sincronización. - VOUT_TRIM_COMMANDO: Comando de calibración del voltaje de salida. - VOUT_MODO_COMMANDO: Comando de selección del modo del voltaje de salida (digital o analógico) . - VOUT_COMMANDO: Comando de programación del voltaje de salida. Control DAC5. - VOUT_MARGEN_ALTO: Voltaje máximo de salida. - VOUT_MARGEN_BAJO: Voltaje mínimo de salida. - VIN_OV_COMMANDO: Control contra sobrevoltajes en V in. - VIN_UV_ALERTA: Control contra bajos voltajes en V in. - PARAM1_COMMANDO: Comando de configuración de parámetros 1. - VPRI_COMMANDO: Parámetro del voltaje de referencia para VPRI. Control DAC3. - ISENSE1A_COMMANDO: Comando de control DAC1 cpu_dac1_reg_1. - ISENSE2A_COMMANDO Comando de control DAC1 cpu_dac1_reg_2. - LEER_VIN: Comando de lectura de la tensión de entrada V in. - LEER_IIN: Comando de lectura de la corriente de entrada Iin. - LEER_IOUT: Comando de lectura corriente media de carga. Estados DAC1 y DAC4. - LEER_VOUT: Comando de lectura de la tensión de salida Vout. - LEER_TEMP: Comando de lectura de la temperatura. - LEER_FLASH_COMMANDO: Comando de lectura de la memoria flash. - ESCRIBIR_FLASH_COMMANDO: Comando de escritura de la memoria flash. - VERSION DE FIRMWARE: Versión de firmware. - VERSION DE HARDWARE: Versión de hardware. La fase configuración se realiza exclusivamente sobre la CPU1. Los comandos programados tienen un efecto funcional en la CPU2, y su configuración se realiza sobre los DACs y los parámetros de control del lazo de control. Una vez que el sistema se encuentra programado y configurado, a partir de los componentes de hardware seleccionados, la siguiente fase de funcionamiento es el control de la carga de la batería, descrito anteriormente. Tanto la CPU1 como la CPU2 encuentran su limitación en el set de instrucciones implementado. A continuación, se detallan las instrucciones mínimas necesarias propuestas para las CPUs: - AND: Operación lógica AND. - OR: Operación lógica OR. - SUB: Operación Resta. - ADD/ADDC: Operación Suma / Suma con retorno de Carro. - CMP: Operación de comparación. - MOV: Operación de mover. - SHIFTING: Mover bits a la izquierda o derecha. - CLR: Operación Limpieza de registro. - MULT/DIV (solo CPU2) : Multiplicación y división. - CALL/STEP/RETURN: Funciones de salto a direcciones de memoria. - LW/SW: Funciones de carga y guardado de información. El controlador flyback 10 tiene también una fase de protección, la cual tiene la función de analizar el funcionamiento del sistema ante fallos. Esta programación se realiza a partir de los siguientes comandos, a partir del uso de la CPU1 y su alojamiento en la región de memoria compartida entre la CPU1 y CPU2: - VOUT_OV_FALLO: Protección contra sobrevoltajes. - VOUT_ALERTA: Aviso de alcance de sobrevoltaje. - IPRI_OC_FALLO: Protección contra sobre corrientes primario y secundario. - ISEC_OC_FALLO: Protección contra sobre en el secundario. - VIN_OV_ALERTA: Control contra altos voltajes en la tensión de entrada V in. - VIN_UV_ALERTA: Control contra bajos voltajes en la tensión de entrada V in. - STATUS CMD: Comando de estado del sistema. - TEMP_OTP_FALLO: Comando de detección de sobre-temperatura. Dicha monitorización y control se realiza a partir de la CPU2. El estado de fallo se muestra mediante el uso del pin PG ("Power Good", Figura 3) , o mediante la lectura del comando STATUS_CMD, el cual actualiza la región de memoria compartida entre la CPU1 y CPU2, cuya lectura es posible a partir del bus de comunicación de la CPU1. La configuración de dichos comandos depende de la configuración del sistema, así como de su entorno de aplicación. La Figura 23 muestra un diagrama de flujo de un algoritmo de protección de acuerdo a una realización. Una vez que el temporizador de control de lectura del ADC se activa, la CPU2 lee el estado de los valores de entrada de los pines VINSENSE, VOUTSENSE, TSENSE, o ADJ, a partir del control del multiplexor reg_mux_adc_ctrl. Una vez que los voltajes se han procesado, la CPU2 revisa el valor de dichos rangos a partir de los valores pre-programados a través de la CPU1 y los comandos VIN_OV_ALERTA, VIN_UV_ALERTA o TEMP_OTP_FALLO, los fallos son activados en valor STATUS_CMD, el cual es leído a partir de la CPU1. El controlador flyback 10 tiene también una fase de sincronización, la cual tiene como función la sincronización de diferentes controladores flyback 10 en paralelo para incrementar el rango de corriente de carga o proporcionar un funcionamiento continuo durante la fase de carga. Tal y como se muestra en la Figura 3, el modo de sincronización propuesto se realiza mediante los pines SYNCIN (para su conexión con una unidad de procesado maestro 50 o un controlador flyback maestro) y SYNCOUT (para su conexión con un controlador flyback esclavo 51) . Dicho modo de sincronización se realiza mediante la selección de dicho valor en el comando OPERACIÓN establecido en la fase de configuración. La lectura de la señal SYNCIN se realiza mediante interrupciones por flanco de subida y bajada sobre la CPU2, y su transmisión directa sobre el bloque PWM, cpu_sincin_isr, tal y como se muestra en la Figura 24, que describe el bloque GPIO 24 y PWM 21. La generación de SYNCOUT se realiza a partir de la CPU2 14 y el valor leído de VOUTSENSE en relación al comando VOUT_COMMANDO programado en la región de memoria compartida. La señal de transmisión sobre PWM1 se transmite sobre la señal SYNCOUT de manera simultánea. La señal SYNCOUT se pude multiplexar para salida directa de PWM1 o a partir de la CPU. Dicha mutiplexión se realiza a partir de cpu_syncout_mux. Como se muestra en las Figuras 25A y 25B, donde se describe el modo de sincronización, la fase de sincronización solo se puede realizar durante la fase de carga hasta un determinado porcentaje determinado por VOUT_COMMANDO. Cuando cada controlador detecta un voltaje superior, desactiva, y realiza el control por voltaje para evitar la sobrecarga o dañado de células de carga. La Figura 26 muestra el funcionamiento del sistema de sincronización, con el encendido y apagado de los transistores Q1 y Q2 en función del valor de la señal SYNCIN. El convertidor flyback 10 de la presente invención se puede emplear en múltiples aplicaciones. En la Figura 27 se muestran varios controladores flyback (10e, 10f, 10g, 10h) en una aplicación en radio frecuencia o la determinada por la Figura 2C. La sincronización de la conducción del transistor Q1 del primario y el elemento de conducción del secundario permite incrementar la corriente de carga de una manera más eficiente, sin el diseño de un nuevo transformador. Esta sincronización se realiza a partir de las señales SYNCIN/SYNCOUT, como se detalla en la Figura 2D, y los modos de sincronización se detallan en las Figuras 2E y 2F. El estado general del sistema se realiza a partir del pin PG (Power Good) , en uso de un pin digital, lo cual permite una respuesta más rápida ante un fallo. En la Figura 28 varios controladores flyback (10a, 10b) se aplican en un sistema de balance de baterías. Los sistemas de carga de alto voltaje están formados por paquetes de células. Cada paquete posee múltiples células configuradas en serie y paralelo. Esta división de células hace que el voltaje objetivo del bloque completo no se realice de manera uniforme, por lo cual los paquetes y células pueden desequilibrarse. La división de reguladores en paquetes permite una carga más eficiente del bloque completo de células. Esta división requiere la implementación de múltiples reguladores flyback para diferentes rangos de voltaje. Como se detalla en la ilustración, estos reguladores se pueden sincronizar para cargar el sistema de una manera más eficiente mediante señales digitales (SYNCIN y SYNCOUT) . El estado general del sistema se realiza a partir de pin PG (Power Good) , en uso de un pin digital, lo cual permite una respuesta más rápida ante un fallo. La realización de la Figura 29 es similar a la mostrada en la Figura 2G. Por último, la realización de la Figura 30 muestra la aplicación en un sistema de aprovechamiento de energía solar, determinado por el circuito de la Figura 2C. Los sistemas de carga solar no poseen un flujo de corriente constante, de forma que en instantes del día durante altas horas de radiación solar la adaptación del bloque ISENSE1 y ISENSE2 se ha e modificar para cargar el elemento de carga de una manera más eficiente. Esta capacidad de no poder generar energía de manera continua requiere el uso de un sistema de almacenamiento intermedio. Este control del estado externo del sistema se realiza con la unidad de procesado maestro 50 (o una unidad de control y regulación) , y su comunicación a partir del bloque SCI y la CPU1.

Publicaciones:

ES2958838 (15/02/2024) - A1 Solicitud de patente con informe sobre el estado de la técnica

Eventos:

En fecha 19/07/2022 se realizó Registro Instancia de Solicitud

En fecha 19/07/2022 se realizó Admisión a Trámite

En fecha 19/07/2022 se realizó 1001P_Comunicación Admisión a Trámite

En fecha 29/07/2022 se realizó Suspenso en examen de oficio

En fecha 29/07/2022 se realizó 6101P_Notificación defectos en examen de oficio

En fecha 04/08/2022 se realizó Publicación Defectos en examen de oficio

En fecha 31/08/2022 se realizó 3007_Registro contestación al suspenso en examen de oficio

En fecha 23/09/2022 se realizó Superado examen de oficio

En fecha 16/02/2023 se realizó Realizado IET

En fecha 21/02/2023 se realizó 1109P_Comunicación Traslado del IET

En fecha 19/09/2023 se realizó PETEX_Petición de examen sustantivo

En fecha 15/02/2024 se realizó Publicación Solicitud

En fecha 15/02/2024 se realizó Publicación Folleto Solicitud con IET (A1)

Pagos:

19/07/2022 - Pago Tasas IET

+ ES-2958838_A11. Un controlador flyback (10) , configurada para la regulación de una fuente de alimentación flyback (1) que incluye un transformador (T1) y un transistor (Q1) regulado por el controlador flyback (10) , caracterizado por que el controlador flyback (10) comprende: - una primera unidad central de procesado (13) y una segunda unidad central de procesado (14) , encargadas de controlar el funcionamiento del controlador flyback (10) en tiempo real; - una memoria (15) , encargada de almacenar datos en tiempo real y el programa de ejecución de las unidades centrales de procesado (13, 14) ; - un primer bloque de muestreo de corriente (17a) , encargado de medir la corriente en el primario del transformador (T1) para su procesado por la segunda unidad central de procesado (14) ; - un bloque de muestreo de tensión de entrada (18) , encargado de la lectura y adaptación del voltaje de entrada en el primario del transformador (T1) para su procesado por la segunda unidad central de procesado (14) ; - un bloque de muestreo de tensión de salida (19) , encargado de la lectura y adaptación del voltaje de salida en el secundario del transformador (T1) para su procesado por la segunda unidad central de procesado (14) ; - un bloque de muestreo de temperatura (20) , encargado de la lectura y adaptación de la temperatura del transformador (T1) para su procesado por la segunda unidad central de procesado (14) ; - un bloque de modulación por ancho de pulsos (21) , encargado de la sincronización y control de moduladores de ancho de pulso a partir de un voltaje objetivo; - un bloque de control de tensión del transformador (22) , encargado de controlar el voltaje en el primario del transformador (T1) para evitar la saturación del primario de transformador (T1) o del transistor (Q1) ; y - una unidad de comunicación (23) , encargada de comunicar la primera unidad central de procesado (13) con una unidad de procesado maestro (50) externa para recibir unos comandos de control. 2. El controlador flyback según la reivindicación 1, caracterizado por que está configurado ara el control de la tensión de un actuador piezoeléctrico (2) . 3. El controlador flyback según la reivindicación 1, caracterizado por que está configurado para el control de la carga de una batería (9) mediante su conexión en paralelo con al menos un controlador flyback adicional (10b) . 4. El controlador flyback según la reivindicación 3, caracterizado por que comprende una unidad de sincronización (6) encargada de la sincronización, en fase o desfase, con el al menos un controlador flyback adicional (10b) mediante el uso de una señal de sincronización (SYNCIN) . 5. El controlador flyback según la reivindicación 3 o 4, caracterizado por que comprende un segundo bloque de muestreo de corriente (17b) , encargado de monitorizar la corriente de carga en el secundario del transformador (T1) , a partir de las mediciones de un sensor de efecto Hall (4) , para su procesado por la segunda unidad central de procesado (14) . 6. El controlador flyback según la reivindicación 5, caracterizado por que la segunda unidad central de procesado (14) está configurada para controlar la corriente en el primario y en el secundario del transformador (T1) mediante la activación de interrupciones cuando se sobrepasa un límite de corriente (IPRI_LIMIT, ISEC_LIMIT) programado. 7. Un sistema de carga de baterías (8) , caracterizado por que comprende una pluralidad de controladores flyback (10a, 10b; 10c, 10d) según la reivindicación 1. 8. El sistema de carga de baterías según la reivindicación 7, caracterizado por que comprende: - una pluralidad de fuentes de alimentación flyback (1a, 1b) conectadas en paralelo alimentando una batería (9) , donde cada fuente de alimentación flyback (1a, 1b) comprende un controlador flyback (10a, 10b) según la reivindicación 1, y donde cada controlador flyback (10a, 10b) comprende una unidad de sincronización (6) encargada de la sincronización, en fase o desfase, entre los controladores flyback (10a, 10b) mediante el uso de una señal de sincronización (SYNCIN) ; y - una unidad de procesado maestro (50) encargada del control de la carga de la batería (9) mediante el envío de unos comandos de control a la unidad de comunicación (23) de los controladores flyback (10a, 10b) . 9. El sistema de carga de baterías según la reivindicación 8, donde los controladores flyback (10a, 10b) de las fuentes de alimentación flyback (1a, 1b) comprenden un segundo bloque de muestreo de corriente (17b) , encargado de monitorizar la corriente de carga en el secundario del transformador (T1) a partir de las mediciones de un sensor de efecto Hall (4) . 10. El sistema de carga de baterías según la reivindicación 7, caracterizado por que comprende: - un primer controlador flyback (10c) conectado al primario del transformador (T1) y con un bloque de muestreo de tensión de entrada (18) para la lectura del voltaje de entrada en el primario del transformador (T1) ; - un segundo controlador flyback (10d) conectado al secundario del transformador (T1) y con un bloque de muestreo de tensión de salida (19) para la lectura del voltaje de salida en el secundario del transformador (T1) ; - unas unidades de procesado maestro (50c, 50d) conectadas a las respectivas unidades de comunicación (23) de los controladores flyback (10c, 10d) y encargadas del control de la carga de la batería (9) mediante el envío de unos comandos de control a los controladores flyback (10c, 10d) ; y donde cada controlador flyback (10c, 10d) comprende una unidad de sincronización (6) encargada de la sincronización entre los controladores flyback (10c, 10d) mediante el uso de unas señales de sincronización (SYNCIN, SYNCOUT) .

Los productos y servicios protegidos por este registro son:

H02M 3/335

Descripciones: