- Home /

- Publicaciones de patentes /

- SISTEMA, MÉTODO Y PROGRAMA DE ORDENADOR PARA DETECCIÓN DE INTERFERENCIAS EN COMUNICACIONES ÓPTICAS

Patente nacional por "SISTEMA, MÉTODO Y PROGRAMA DE ORDENADOR PARA DETECCIÓN DE INTERFERENCIAS EN COMUNICACIONES ÓPTICAS"

Este registro ha sido solicitado por

DATLIGHT, S.L.

a través del representanteELI SALIS

Contacto

- Estado: A punto de caducar

- País:

- España

- Fecha solicitud:

- 30/03/2022

- Número solicitud:

-

P202230289

- Número publicación:

-

ES2953591

- Fecha de concesión:

-

- Inventores:

-

Persona física

- Datos del titular:

-

DATLIGHT, S.L.

- Datos del representante:

-

Eli SALIS

- Clasificación Internacional de Patentes:

- H04B 10/07

- Clasificación Internacional de Patentes de la publicación:

- H04B 10/07

- Fecha de vencimiento:

Quiero registrar una patente

Reivindicaciones:

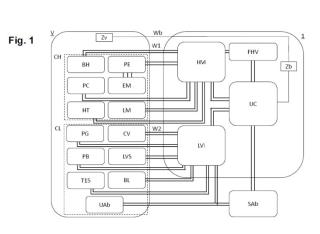

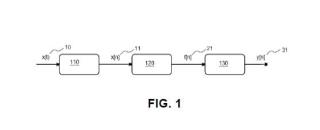

+ ES-2953591_A11. Sistema para detección de interferencias en comunicaciones ópticas, caracterizado porque comprende un filtro adaptado (120) configurado para eliminar interferencias causadas por una o más fuentes de luz en una señal digital recibida (11) mediante la realización de una operación de filtrado sobre dicha señal digital recibida (11) , en donde la señal digital recibida (11) comprende un patrón de pulsos, aleatorio y desconocido, emitido a través de un canal óptico, y en donde la operación de filtrado comprende aplicar un filtrado paso bajo adaptado a dicho patrón de pulsos y correlacionar e invertir en el tiempo el patrón de pulsos con la señal digital recibida (11) . 2. Sistema según la reivindicación 1, en donde el filtro adaptado (120) está incluido en un receptor que comprende, además, un conversor analógico digital (110) configurado para recibir una señal analógica (10) y convertirla en dicha señal digital (11) . 3. Sistema según una cualquiera de las reivindicaciones anteriores, que comprende, además, un muestreador (130) , dispuesto a la salida del filtro adaptado (120) , y configurado para sincronizar unas señales de captura de muestreo de una señal de salida (31) del filtro adaptado (120) , tanto para una frecuencia como una fase de la señal de salida. 4. Sistema según la reivindicación 3, en donde el muestreador (130) está configurado para realizar la sincronización de la fase de la señal de salida mediante la implementación de un algoritmo que calcula un error de fase entre las señales de captura de muestreo y una señal de captura de muestreo óptima, y realiza un desplazamiento de la fase de muestreo hasta que las señales de captura de muestreo se realicen en un instante de muestreo de máxima relación señal a ruido. 5. Sistema según la reivindicación 1, en donde el filtro adaptado (120) está implementado mediante un procesador de señal digital, DSP. 6. Sistema según la reivindicación 3, en donde el filtro adaptado (120) y el muestreador (130) están implementados mediante un procesador de señal digital, DSP. 7. Método para detección de interferencias en comunicaciones ópticas, caracterizado porque comprende eliminar, utilizando un filtro adaptado (120) , interferencias causadas por una o más fuentes de luz en una señal digital recibida (11) , mediante la realización de una operación de filtrado sobre dicha señal digital recibida (11) , en donde la señal igital recibida (11) comprende un patrón de pulsos, aleatorio y desconocido, emitido a través de un canal óptico, y en donde la operación de filtrado comprende aplicar un filtrado paso bajo adaptado a dicho patrón de pulsos y correlacionar e invertir en el tiempo el patrón de pulsos con la señal digital recibida (11) . 8. Método según la reivindicación 7, en donde la operación de filtrado comprende: acumular, mediante un módulo acumulador (121) , la señal digital recibida (11) para un determinado orden; normalizar dicha acumulación mediante un módulo divisor (122) ; y acondicionar unos valores de salida del módulo divisor mediante un módulo de mapeo (123) . 9. Método según la reivindicación 7 u 8, en donde el filtro adaptado (120) está incluido en un receptor que comprende, además, un conversor analógico digital (110) que recibe una señal analógica (10) y la convierte en dicha señal digital (11) . 10. Método según la reivindicación 9, en donde la señal analógica (10) , previamente a la conversión, es escalada y adaptada a unos determinados valores de potencia. 11. Método según una cualquiera de las reivindicaciones anteriores 7-10, que comprende, además, sincronizar, por un muestreador (130) , unas señales de captura de muestreo de una señal de salida (31) del filtro adaptado (120) , tanto para una frecuencia como una fase de la señal de salida. 12. Método según la reivindicación 11, que comprende realizar la sincronización de la fase de la señal de salida (31) mediante la implementación de un algoritmo que calcula un error de fase entre las señales de captura de muestreo y una señal de captura de muestreo óptima y realiza un desplazamiento de la fase de muestreo hasta que las señales de captura de muestreo se realicen en un instante de muestreo de máxima relación señal a ruido. 13. Método según la reivindicación 7, en donde el filtro adaptado (120) está implementado mediante un procesador de señal digital, DSP. 14. Método según la reivindicación 11, en donde el filtro adaptado (120) y el muestreador (130) están implementados mediante un procesador de señal digital, DSP. 15. Producto de programa de ordenador que incluye instrucciones de código que cuando se ejecutan en un sistema de computación implementan un método según una cualquiera de las reivindicaciones 7 a 14.

Los productos y servicios protegidos por este registro son:

H04B 10/07

Descripciones:

+ ES-2953591_A1 SISTEMA, MÉTODO Y PROGRAMA DE ORDENADOR PARA DETECCIÓN DE INTERFERENCIAS EN COMUNICACIONES ÓPTICAS Campo de la técnica La presente invención concierne a un sistema, un método y un producto de programa de ordenador para detección de interferencias, particularmente ruido blanco aditivo y gaussiano, en comunicaciones ópticas (es decir, a través de luz) entre un emisor y un receptor. Antecedentes de la invención En el estado de la técnica se conocen algunos filtros adaptados. Por ejemplo, la patente US10866304B1 divulga la utilización de un filtro adaptado para detección de señal que maximiza la SNR y obtiene un vector de N dimensiones con elementos medidos en cada antena. La patente EP1071966B1 divulga un filtro adaptado para señales GPS. Por las patentes o solicitudes de patente EP2777178B1, WO2022/039758, US7463181B2, US8483578B2, US6297764B1 y US10039498B2 se conocen otros sistemas/dispositivos de filtrado, ópticos, para eliminación de diferentes tipos de interferencias. A pesar de que existen filtros adaptados para múltiples sectores, todavía se requieren nuevos sistemas/métodos para detección de interferencias en comunicaciones ópticas. Exposición de la invención A tal fin, ejemplos de realización de la presente invención aportan, de acuerdo a un primer aspecto, un sistema para detección de interferencias en comunicaciones ópticas. El sistema incluye un filtro adaptado configurado para eliminar interferencias causadas por una o más fuentes de luz en una señal digital recibida mediante la realización de una operación de filtrado sobre dicha señal digital recibida. La señal digital recibida comprende un patrón de pulsos, aleatorio y desconocido, emitido a través de un canal óptico, y la operación de filtrado comprende aplicar un filtrado paso bajo adaptado al atrón de pulsos y correlacionar e invertir en el tiempo el patrón de pulsos con la señal digital recibida. Ejemplos de realización de la presente invención también proporcionan, según un segundo aspecto, un método para detección de interferencias en comunicaciones ópticas. El método comprende eliminar, utilizando un filtro adaptado, interferencias causadas por una o más fuentes de luz en una señal digital recibida, mediante la realización de una operación de filtrado sobre dicha señal digital recibida, en donde la señal digital recibida comprende un patrón de pulsos, aleatorio y desconocido, emitido a través de un canal óptico, y en donde la operación de filtrado comprende aplicar un filtrado paso bajo adaptado a dicho patrón de pulsos y correlacionar e invertir en el tiempo el patrón de pulsos con la señal digital recibida. Según la presente invención, el filtro adaptado está incluido en un receptor, y particularmente está implementado mediante un procesador de señal digital (DSP) . En un ejemplo de realización, la operación de filtrado comprende, además: acumular, mediante un módulo acumulador, la señal digital recibida para un determinado orden; normalizar dicha acumulación mediante un módulo divisor; y acondicionar unos valores de salida del módulo divisor mediante un módulo de mapeo. En un ejemplo de realización, el sistema incluye también un conversor analógico digital configurado para recibir una señal analógica y convertirla en dicha señal digital. En algunos ejemplos, la señal analógica, previamente a la conversión, es escalada y adaptada a unos determinados valores de potencia. En un ejemplo de realización, el sistema incluye también un muestreador, dispuesto a la salida del filtro adaptado, y configurado para sincronizar unas señales de captura de muestreo de una señal de salida del filtro adaptado, tanto para una frecuencia como una fase de la señal de salida. En un ejemplo de realización, el muestreador está configurado para realizar la sincronización de la fase de la señal de salida mediante la implementación de un algoritmo que calcula un error de fase entre las señales de captura de muestreo y una señal de captura de muestreo óptima, y realiza un desplazamiento de la fase de muestreo hasta que las señales de captura de muestreo se realicen en un instante de muestreo de máxima relación señal a ruido. Particularmente, el muestreador también está implementado mediante un DSP. Otras realizaciones de la invención que se describen en el presente documento incluyen también productos de programas de ordenador o informáticos para realizar las etapas y operaciones del método propuesto en el segundo aspecto de la invención. Más particularmente, un producto de programa de ordenador es una realización que tiene un medio legible por ordenador que incluye instrucciones de programa informático codificadas en el mismo que cuando se ejecutan en al menos un procesador de un sistema informático producen al procesador realizar las operaciones indicadas en el presente documento como realizaciones de la invención. Por lo tanto, la presente invención es capaz de detectar un patrón conocido en una señal aleatoria y desconocida, maximizando la relación señal a ruido en un instante de muestreo determinado y cuya muestra será la que posteriormente habrá a la entrada de un decisor. Por ello, es muy útil para detectar los patrones, que en este caso serán los pulsos generados por el transmisor y emitidos al canal. Asimismo, la presente invención permite maximizar la SNR en presencia de ruido blanco aditivo y gaussiano, en comunicaciones ópticas, LIFI (Light Fidelity) en entornos exteriores y en movimiento. Lo que permite mejorar la señal de datos, aumentando la distancia de comunicación en comparación con los esquemas convencionales. El filtro adaptado propuesto es de particular relevancia en comunicaciones entre dos vehículos (V2V) o entre vehículos e infraestructuras (V2I) , eliminando por completo las interferencias introducidas por otras fuentes luminosas, incluida la peor de las interferencias, la solar. Igualmente, el filtro adaptado puede utilizarse en comunicaciones subacuáticas, de interior, o incluso la implantación de comunicaciones LIFI en vehículos aéreos, los cuales están enormemente limitados por las interferencias de radiofrecuencia. Breve descripción de los dibujos Las anteriores y otras características y ventajas se comprenderán más plenamente a partir de la siguiente descripción detallada de unos ejemplos de realización, meramente ilustrativa y no limitativa, con referencia a los dibujos que la acompañan, en los que: La Fig. 1 es un diagrama de bloques de un sistema para detección de interferencias en comunicaciones ópticas, según un ejemplo de realización de la presente invención. La Fig. 2 ilustra un ejemplo de una señal que puede ser transmitida al sistema propuesto. La Fig. 3 ilustra el comportamiento de cada bloque del sistema para una SNR en recepción de 25dB. La Fig. 4 ilustra el comportamiento de cada bloque del sistema para una SNR en recepción de 0dB. La Fig. 5 ilustra el comportamiento de cada bloque del sistema para una SNR en recepción de -10dB. La Fig. 6 ilustra diferentes casos de muestreo utilizando el algoritmo Early-late, según un ejemplo de realización de la presente invención. La Fig. 7 ilustra diferentes casos de muestreo utilizando el algoritmo Gardner, según un ejemplo de realización de la presente invención. La Fig. 8 ilustra otro ejemplo de realización del sistema propuesto. La Fig. 9 ilustra, esquemáticamente, el filtro adaptado, según un ejemplo de realización de la presente invención. La Fig. 10 ilustra, esquemáticamente, el módulo acumulador, según un ejemplo de realización de la presente invención. La Fig. 11 es un esquemático del corte (slice) DSP equivalente al módulo divisor, según un ejemplo de realización de la presente invención. La Fig. 12 ilustra, esquemáticamente, el módulo de mapeo, según un ejemplo de realización de la presente invención. La Fig. 13 ilustra, esquemáticamente, el muestreador, según un ejemplo de realización de la presente invención. La Fig. 14 ilustra, esquemáticamente, el módulo limitador, según un ejemplo de realización de la presente invención. La Fig. 15 ilustra, esquemáticamente, el módulo contador, según un ejemplo de realización de la presente invención. La Fig. 16 ilustra, esquemáticamente, el módulo comparador 1, o CMP1, mientras que la Fig. 17 ilustra el módulo comparador 2, o CMP2, según unos ejemplos de realización de la presente invención. La Fig. 18 ilustra, esquemáticamente, el módulo error, según un ejemplo de realización de la presente invención. La Fig. 19 es un esquemático del corte DSP del módulo error, según un ejemplo de realización de la presente invención. Descripción detallada de la invención y de unos ejemplos de realización La presente invención proporciona un sistema y un método para detección de interferencias (causadas por cualquier fuente de luz, o incluso interferencia debidas a la luz solar) en comunicaciones ópticas. En particular, la presente invención es muy eficaz para maximizar la SNR ante la presencia de ruido blanco, es decir, ruido cuyas muestras no mantienen correlación estadística en el dominio del tiempo, y por tanto su densidad espectral de potencia es constante. Para ello, la presente invención incluye/implementa un filtro adaptado (o matched filter) , lineal. El filtro adaptado (120) , particularmente implementado mediante software, por ejemplo, mediante un procesador de señal digital (DSP) , tal y como se explicará más adelante, mediante la realización de una operación de filtrado es capaz de detectar un patrón conocido en la señal aleatoria y desconocida recibida. Para ello, particularmente se correla el patrón que se quiere detectar invertido en el tiempo con la señal desconocida, o lo que es lo mismo, se convoluciona la señal desconocida con el patrón conocido conjugado e invertido en el tiempo. De esta forma, si se define la forma de pulso en transmisión como: Entonces, la respuesta ideal del filtro adaptado (120) es: Suponiendo una señal recibida x (t) , y teniendo en cuenta que aplicar el filtro adaptado (120) a dicha señal es equivalente a realizar una convolución entre la señal y el filtro, se puede calcular la expresión de la salida del filtro adaptado (120) como: Donde y (t) representa la salida del filtro adaptado (120) en el instante T. Teniendo en cuenta que hm (t) = h (T - t) , por tanto, si se sustituye en la ecuación 1.3, se obtiene la siguiente equivalencia: La expresión 1.4 se ha derivado de las expresiones 1.2 y 1.3, y equivale a la correlación cruzada de la señal recibida x (t) y el pulso en transmisión en el instante T. Este comportamiento del filtro adaptado (120) proporciona dos grandes ventajas. Por un lado, las formas de pulso generalmente están compuestas por bajas frecuencias, por tanto, la aplicación de un filtrado paso bajo a la señal en recepción permite el paso a estas formas de pulso que contienen la información relevante y atenúa las altas frecuencias que únicamente contienen ruido. La otra ventaja es la correlación que realiza el filtro de la señal en recepción con la forma de pulso en transmisión, detectando así cuando la señal recibida coincide con el patrón conocido. Con referencia ahora a la Fig. 1, en la misma se muestra un diagrama de bloques del sistema propuesto, según un ejemplo de realización. En este ejemplo, se ilustra un conversor analógico-digital de entrada (110) , el filtro adaptado (120) a la forma de pulso hm[n], y un bloque muestreador (130) , que se encarga de conseguir la recuperación de la sincronización. En las Figs. 3-5 se muestran varios ejemplos de la SNR en recepción utilizando el sistema anterior. En la Fig. 3, se ha simulado una SNR en recepción de 25dB. En la figura se puede ver una ligera oscilación en la señal recibida x (t) (10) (ver Fig.2 para un ejemplo de la misma) , debido al ruido añadido. En la señal de salida del filtro adaptado (120) f[n] (21) se genera el resultado de la acumulación durante el período completo. Finalmente, el muestreador (130) captura las muestras en los instantes óptimos, nT, de máxima SNR. La recuperación de los datos es correcta. En la Fig. 4, se muestra la misma simulación para una SNR en recepción de 0dB. Si se observa la señal recibida aparece muy distorsionada, sin embargo, el filtro adaptado (120) recupera correctamente los datos originales, en los instantes de máxima SNR. La recuperación sigue siendo correcta. En la Fig. 5, se muestra la misma simulación para una SNR en recepción de -10dB. La señal recibida ya es totalmente irreconocible de forma visual, el filtro adaptado (120) ecupera correctamente los datos originales, pero con mayor dificultad. Por ejemplo, la muestra capturada en el instante t = 3T, podría tener un valor aproximado de 0.5V, lo que se interpretaría correctamente por el decisor como un nivel alto, pero la diferencia es mucho menor que en la simulación con una SNR de 25dB. La recuperación sigue siendo correcta. En algunos ejemplos de realización, se realiza, preferiblemente en la parte analógica, una etapa de control automático de ganancia. Esta etapa se encarga de escalar, de forma automática y adaptada, la señal recibida (10) a unos valores de potencia conocidos. De esta manera, si la señal recibida (10) tiene una potencia demasiado alta se evita la introducción de distorsión (clipping) por el conversor analógico-digital (110) ; por el contrario, si la señal recibida (10) tiene una potencia demasiado baja se evita una pérdida de precisión a la hora de recuperar la información relevante. El bloque muestreador (130) , es el encargado de la recuperación de sincronización tanto en frecuencia, como en fase. La frecuencia en transmisión es conocida por el receptor, la sincronización en fase, en cambio, es desconocida y debe tenerse en cuenta. En un ejemplo de realización, para conseguir la sincronización en fase se desplaza la fase de muestreo sobre la salida (21) del filtro adaptado (120) hasta que las capturas se realicen en los instantes de máxima relación señal a ruido o SNR. Para ello, por un lado, se mide el error en fase que se está cometiendo entre la captura realizada y la captura óptima, es decir, se realiza la corrección de fase sobre la señal de muestreo. Por otro lado, se desplaza la fase de muestreo. De estas dos tareas se encarga el bloque muestreador (130) . En un ejemplo de realización, para medir el error en fase que se está cometiendo en el muestreo se utiliza un algoritmo de recuperación de sincronización, tal y como el algoritmo Early-late gate o el algoritmo Gardner. El algoritmo Early-late calcula el error a partir de muestras que están adelantadas y atrasadas respecto al punto de muestreo ideal. Para implementar este algoritmo es necesario tomar 3 muestras en cada período de símbolo, la muestra adelantada, la atrasada y la salida (31) del filtro adaptado (120) que es la que cae en medio. Para calcular el error se puede utilizar la siguiente ecuación: La salida de este algoritmo es la muestra yn_1. En la Fig. 6, aparecen 6 casos de muestreo con el algoritmo Early-late. Los 3 casos superiores ( (a) muestreo adelantado, (b) atrasado y (c) óptimo, respectivamente) son casos en los que el cálculo del error se realiza sobre un pico positivo, los 3 inferiores ( (d) muestreo adelantado, (e) atrasado y (f) óptimo, respectivamente) sobre un pico negativo. Para estos ejemplos se ha supuesto una señal bipolar de ±1V. Si se calcula el error que devuelve la ecuación del algoritmo Early-late para cada uno de los ejemplos en las figuras, se obtienen los siguientes resultados: De esta forma, se puede concluir que haciendo uso del algoritmo Early-Late, la corrección que se debe realizar a la fase de muestreo es el valor devuelto por la ecuación 1.5, aplicando la correspondiente normalización en amplitud. El algoritmo de Gardner está muy extendido y es frecuente su uso en sistemas de recuperación de sincronismo. Gardner utiliza 2 muestras por período de símbolo y para calcular el error utiliza la ecuación 1.5, al igual que el algoritmo Early-late. La salida de este algoritmo es la muestra yn . La separación temporal entre las muestras exteriores, y 2 es de un período de bit, y la separación temporal entre las muestras consecutivas, es de medio período de bit. Es importante destacar que la ecuación de Gardner necesita muestrear sobre una señal bipolar para que el error calculado sea correcto. En la Fig. 7 se pueden observar 6 casos de muestreo con el algoritmo de Gardner. Los 3 casos superiores ( (a) muestreo adelantado, (b) atrasado y (c) óptimo, respectivamente) son casos en los que el cálculo del error se realizará sobre una pendiente negativa, los 3 inferiores ( (d) muestreo adelantado, (e) atrasado y (f) óptimo, respectivamente) son casos con pendiente positiva. Para estos ejemplos se ha supuesto una señal bipolar de ±1 V. Si se calcula el error que devuelve la ecuación de Gardner para cada uno de los ejemplos en las figuras, se obtienen los siguientes resultados: El resultado de las ecuaciones aporta dos datos importantes, uno es la amplitud del error que se está cometiendo en el muestreo y el otro es el signo del error, que revelará la dirección en la que se deberá corregir la fase de muestreo. En el caso de Gardner, el signo que devuelve la ecuación del error es contrario al signo del incremento a realizar sobre la fase de muestreo. De esta forma, se puede concluir que haciendo uso del algoritmo Gardner, la corrección que se debe realizar a la fase de muestreo es la negación del valor devuelto por la ecuación 1.5, aplicando la correspondiente normalización en amplitud. Con referencia ahora a la Fig. 8, en la misma se muestra otro ejemplo de realización del sistema propuesto. Según este ejemplo de realización, los datos de entrada (capturados por el citado conversor analógico-digital 110) entran al filtro adaptado (120) para que éste genere una señal de acumulación. El bloque muestreador (130) se encarga de generar durante un período de reloj, tres señales de habilitación de reloj (o clock enable) diferentes, que habilitarán, independientemente, cada uno de los 3 registros que aparecen en paralelo para realizar las diferentes capturas de la salida del filtro adaptado (120) . Como se puede observar, del bloque muestreador (130) salen 3 señales de habilitación de reloj, cada una para capturar las 3 muestras necesarias durante el período de bit y posteriormente calcular el error. El bloque de error 140 aplica la ecuación 1.5, y su salida es capturada por un registro cuando se activa CE2, este registro es útil para evitar los fallos (glitches) que se producen mientras se capturan los datos y se calcula el resultado de la operación. Una vez el error es capturado por el registro, el bloque muestreador (130) realiza un desfase de las tres señales de habilitación de reloj para, iteración tras iteración, converger a una fase óptima de sincronización. Finalmente, la señal MODE sirve para implementar el algoritmo de recuperación de sincronización. El muestreador (130) , alterna entre sumar o restar el error calculado y registrado. El multiplexor alterna la salida del filtro adaptado, pudiendo seleccionar entre la muestra S2 o la muestra S3. En este ejemplo de realización, el filtro adaptado (120) se encarga de acumular la señal de entrada de forma discreta para un orden definido, normalizar esta acumulación y finalmente realizar un mapeo de los datos de salida para acondicionarlos a los bloques posteriores. Estas operaciones están divididas en tres diferentes módulos/bloques, tal y como se muestra en la Fig. 9, particularmente implementados con cortes DSP. El módulo o bloque acumulador (121) se encarga de implementar la ecuación 1.6, que es la expresión equivalente a un acumulador de orden N, donde x[n] es la entrada, acc[n] es la acumulación realimentada y y[n] la salida: La implementación de dicha expresión matemática da como resultado el esquemático que se muestra en la Fig. 10. Para implementar este esquemático, se debe hacer uso de un registro de desplazamiento capaz de almacenar las muestras retrasadas en el tiempo, además de un corte DSP que se encargará de realizar la suma y resta necesaria. El módulo o bloque divisor (122) permite normalizar la acumulación. Su funcionamiento se basa en un corte DSP, por lo que se representará el esquemático de la configuración del DSP directamente. Dicho esquemático se puede ver en la Fig. 11. Asimismo, se realiza una multiplicación decimal en punto flotante para poder normalizar. Suponiendo la expresión (1.7) como la salida del módulo acumulador (121) en la que acc representa la acumulación, N el orden del filtro y x el dato de entrada, el valor que se desea obtener tras el módulo divisor (122) será el representado por la expresión (1.8) , donde div equivale a la salida del módulo divisor (122) : Para ello, se multiplica la salida del acumulador por un valor constante definido como el inverso del orden del filtro, particularmente desplazado 17 bits a la izquierda. En un ejemplo de realización, según la Fig. 11, la operación equivalente que realiza el corte DSP es: El módulo o bloque de mapeo (123) se encarga de acondicionar los valores de salida del divisor (122) para que sean interpretables de forma correcta por los bloques posteriores. Esta etapa es necesaria debido a que el conversor analógico-digital (110) ofrece valores entre [0, 16383], y la señal de acumulación debe ser bipolar. Por tanto, el mapeo particularmente se realiza desde un dominio [0, 16383] hacia un dominio [8192.- 8191], obteniendo así un escalado bipolar y aprovechando toda la resolución del conversor (110) . La operación matemática que debe realizar este módulo de mapeo (123) aparece reflejada en la ecuación 1.10, donde map representa la salida del módulo de mapeo (123) y div la salida del divisor (122) . La configuración del módulo de mapeo (123) y, por tanto, del DSP asociado a este, se puede ver en la Fig. 12. Se puede observar como la entrada del multiplexor Z es PCIN, es decir, el bus dedicado para interconectar los cortes DSP de forma directa sin rutado adicional, además, está seleccionada con un desplazamiento de 17 bits hacia la derecha, este desplazamiento es necesario para rectificar la operación realizada previamente por el módulo divisor (122) . Con referencia ahora a la Fig. 13, en la misma se ilustra un ejemplo de realización particular del muestreador (130) . El muestreador (130) toma un valor de cuenta límite, e implementa un contador que se incrementa hasta alcanzar dicho valor límite y una vez alcanzado, se reinicia a cero, siendo éste, el período del ciclo de cuenta. Durante cada ciclo de cuenta, se encarga de generar 3 señales activas durante un período de reloj, denominadas CE1, CE2 y CE3, que capturan cada una de las muestras necesarias para calcular el error. Más específicamente, el módulo limitador (131) se encarga de calcular el valor límite de cuenta para cada ciclo, el módulo contador (132) implementa un contador unitario que se resetea cuando alcanza el valor límite proporcionado por el módulo limitador (131) . A través de las señales COUNT1 y COUNT2 se transmite el valor de cuenta a los bloques CMP1 (133) y CMP2 (134) . Estos dos módulos son internamente idénticos y son comparadores que activan su salida cuando sus dos valores de entrada coinciden. La Fig. 14 muestra un ejemplo de realización particular del módulo limitador (131) . Este bloque se encarga de modificar el valor de cuenta límite para cada ciclo, pudiendo así contar un valor mayor o menor al período de bit. El límite de cuenta equivalente al período de bit se le proporciona por la entrada COUNT_LIMIT, de esta forma se consigue esplazar la fase de muestreo hacia delante o hacia atrás. La corrección de fase realizada será el error calculado por el módulo ERROR 140. La entrada MODE sirve para sumar o restar el error de entrada sobre el valor de COUNT_LIMIT, por tanto, permite alternar entre el algoritmo Early-Late y Gardner (es decir, entre un algoritmo de sincronización u otro) . La Fig. 15 muestra un ejemplo de realización particular del módulo contador (132) . Este elemento se encarga de incrementar de forma unitaria un valor de cuenta y ofrecer dicho valor de cuenta a su salida. Además, incluye un detector de patrones configurado para que la cuenta se reinicie a cero cuando alcance el valor COUNT_LIMIT. La propia señal PATTERN DETECT que ofrece el corte DSP es útil para detectar cuando la cuenta ha llegado al límite, precisamente en ese instante es cuando interesa capturar la tercera muestra, por lo tanto, la salida PATTERN DETECT será CE3. Los bloques comparadores CMP1 (133) y CMP2 (134) están implementados también sobre cortes DSP. El módulo CMP1 (133) transmite el valor de cuenta a través del bus PCIN interno, al módulo CMP2 (134) , de forma que ambos conocen el valor de cuenta. Internamente, cada comparador compara el valor de cuenta con el valor de threshold o límite que tiene a su entrada, de esta forma, si se diseñan los valores de threshold, tal y como se muestra en la Fig. 13, se consigue que el comparador CMP1 (133) se active justo al inicio de cada ciclo y el comparador CMP2 (134) se active justo en la mitad. Estas señales serán CE1 y CE2 respectivamente. En la Figs. 16 y 17 se pueden ver las configuraciones de los cortes DSP correspondientes a los bloques CMP1 y CMP2 respectivamente. Con referencia ahora a las Figs. 18 y 19, en las mismas se ilustra unos ejemplos del bloque error (140) . Este módulo (140) está formado por un único corte DSP y se encarga de calcular el error a partir de las tres muestras capturadas sobre la señal de acumulación del pulso. Para ello, implementa la ecuación (1.5) y ofrece a su salida el resultado de dicha ecuación dividido por un valor potencia de 2 configurable. Preferiblemente, este factor es potencia de 2 para que la división se pueda implementar de forma sencilla como desplazamiento de bits. En dichas figuras, se presentan tres muestras como entrada y el error calculado como salida. Las operaciones que realiza el bloque error (140) son la ecuación del error en el corte DSP y posteriormente el desplazamiento para dividir. Para generalizar el valor de division DIV, se utiliza la siguiente ecuación: La invención propuesta puede implementarse en hardware, software, firmware o cualquier combinación de los mismos. Si se implementa en software, las funciones pueden almacenarse en o codificarse como una o más instrucciones o código en un medio legible por ordenador. Como se usa en el presente documento, los productos de programa de ordenador que comprenden medios legibles por ordenador incluyen todas las formas de medio legible por ordenador excepto, hasta el punto de que ese medio se considere que no son señales de propagación transitorias no establecidas. El alcance de la presente invención está definido en las reivindicaciones adjuntas.

Publicaciones:

ES2953591 (14/11/2023) - A1 Solicitud de patente con informe sobre el estado de la técnica

Eventos:

En fecha 30/03/2022 se realizó Registro Instancia de Solicitud

En fecha 31/03/2022 se realizó Admisión a Trámite

En fecha 31/03/2022 se realizó 1001P_Comunicación Admisión a Trámite

En fecha 21/04/2022 se realizó Defectos en solicitud de reducción de tasas

En fecha 21/04/2022 se realizó 6100X_Notificación defectos en solicitud de reducción de tasas

En fecha 27/04/2022 se realizó Publicación defectos en solicitud de reducción de tasas

En fecha 23/06/2022 se realizó 3007_Registro subsanación de defectos en reducción de tasas

En fecha 01/07/2022 se realizó Concesión solicitud de reducción de tasas

En fecha 05/07/2022 se realizó Superado examen de oficio

En fecha 07/07/2022 se realizó Publicación concesión reducción de tasas

En fecha 30/11/2022 se realizó Realizado IET

En fecha 02/12/2022 se realizó 1109P_Comunicación Traslado del IET

En fecha 14/11/2023 se realizó Publicación Solicitud

En fecha 14/11/2023 se realizó Publicación Folleto Solicitud con IET (A1)

En fecha 12/02/2024 se realizó Registro Documentación no Identificada

En fecha 12/02/2024 se realizó 5215P_Observaciones del solicitante al IET, Opinión Escrita y/o alegaciones a observaciones de terceros

En fecha 13/02/2024 se realizó PETEX_Petición de examen sustantivo

En fecha 29/02/2024 se realizó Validación petición y/o pago de examen sustantivo conforme

En fecha 29/02/2024 se realizó El solicitante ha contestado pero existen nuevas objeciones a la concesión de la solicitud

En fecha 29/02/2024 se realizó Elaboración de examen sustantivo

En fecha 29/02/2024 se realizó 6120P_Notificación de examen sustantivo

En fecha 06/03/2024 se realizó Publicación de examen sustantivo

Pagos:

30/03/2022 - Pago Tasas IET

+ ES-2953591_A11. Sistema para detección de interferencias en comunicaciones ópticas, caracterizado porque comprende un filtro adaptado (120) configurado para eliminar interferencias causadas por una o más fuentes de luz en una señal digital recibida (11) mediante la realización de una operación de filtrado sobre dicha señal digital recibida (11) , en donde la señal digital recibida (11) comprende un patrón de pulsos, aleatorio y desconocido, emitido a través de un canal óptico, y en donde la operación de filtrado comprende aplicar un filtrado paso bajo adaptado a dicho patrón de pulsos y correlacionar e invertir en el tiempo el patrón de pulsos con la señal digital recibida (11) . 2. Sistema según la reivindicación 1, en donde el filtro adaptado (120) está incluido en un receptor que comprende, además, un conversor analógico digital (110) configurado para recibir una señal analógica (10) y convertirla en dicha señal digital (11) . 3. Sistema según una cualquiera de las reivindicaciones anteriores, que comprende, además, un muestreador (130) , dispuesto a la salida del filtro adaptado (120) , y configurado para sincronizar unas señales de captura de muestreo de una señal de salida (31) del filtro adaptado (120) , tanto para una frecuencia como una fase de la señal de salida. 4. Sistema según la reivindicación 3, en donde el muestreador (130) está configurado para realizar la sincronización de la fase de la señal de salida mediante la implementación de un algoritmo que calcula un error de fase entre las señales de captura de muestreo y una señal de captura de muestreo óptima, y realiza un desplazamiento de la fase de muestreo hasta que las señales de captura de muestreo se realicen en un instante de muestreo de máxima relación señal a ruido. 5. Sistema según la reivindicación 1, en donde el filtro adaptado (120) está implementado mediante un procesador de señal digital, DSP. 6. Sistema según la reivindicación 3, en donde el filtro adaptado (120) y el muestreador (130) están implementados mediante un procesador de señal digital, DSP. 7. Método para detección de interferencias en comunicaciones ópticas, caracterizado porque comprende eliminar, utilizando un filtro adaptado (120) , interferencias causadas por una o más fuentes de luz en una señal digital recibida (11) , mediante la realización de una operación de filtrado sobre dicha señal digital recibida (11) , en donde la señal igital recibida (11) comprende un patrón de pulsos, aleatorio y desconocido, emitido a través de un canal óptico, y en donde la operación de filtrado comprende aplicar un filtrado paso bajo adaptado a dicho patrón de pulsos y correlacionar e invertir en el tiempo el patrón de pulsos con la señal digital recibida (11) . 8. Método según la reivindicación 7, en donde la operación de filtrado comprende: acumular, mediante un módulo acumulador (121) , la señal digital recibida (11) para un determinado orden; normalizar dicha acumulación mediante un módulo divisor (122) ; y acondicionar unos valores de salida del módulo divisor mediante un módulo de mapeo (123) . 9. Método según la reivindicación 7 u 8, en donde el filtro adaptado (120) está incluido en un receptor que comprende, además, un conversor analógico digital (110) que recibe una señal analógica (10) y la convierte en dicha señal digital (11) . 10. Método según la reivindicación 9, en donde la señal analógica (10) , previamente a la conversión, es escalada y adaptada a unos determinados valores de potencia. 11. Método según una cualquiera de las reivindicaciones anteriores 7-10, que comprende, además, sincronizar, por un muestreador (130) , unas señales de captura de muestreo de una señal de salida (31) del filtro adaptado (120) , tanto para una frecuencia como una fase de la señal de salida. 12. Método según la reivindicación 11, que comprende realizar la sincronización de la fase de la señal de salida (31) mediante la implementación de un algoritmo que calcula un error de fase entre las señales de captura de muestreo y una señal de captura de muestreo óptima y realiza un desplazamiento de la fase de muestreo hasta que las señales de captura de muestreo se realicen en un instante de muestreo de máxima relación señal a ruido. 13. Método según la reivindicación 7, en donde el filtro adaptado (120) está implementado mediante un procesador de señal digital, DSP. 14. Método según la reivindicación 11, en donde el filtro adaptado (120) y el muestreador (130) están implementados mediante un procesador de señal digital, DSP. 15. Producto de programa de ordenador que incluye instrucciones de código que cuando se ejecutan en un sistema de computación implementan un método según una cualquiera de las reivindicaciones 7 a 14.

Los productos y servicios protegidos por este registro son:

H04B 10/07

Descripciones:

+ ES-2953591_A1 SISTEMA, MÉTODO Y PROGRAMA DE ORDENADOR PARA DETECCIÓN DE INTERFERENCIAS EN COMUNICACIONES ÓPTICAS Campo de la técnica La presente invención concierne a un sistema, un método y un producto de programa de ordenador para detección de interferencias, particularmente ruido blanco aditivo y gaussiano, en comunicaciones ópticas (es decir, a través de luz) entre un emisor y un receptor. Antecedentes de la invención En el estado de la técnica se conocen algunos filtros adaptados. Por ejemplo, la patente US10866304B1 divulga la utilización de un filtro adaptado para detección de señal que maximiza la SNR y obtiene un vector de N dimensiones con elementos medidos en cada antena. La patente EP1071966B1 divulga un filtro adaptado para señales GPS. Por las patentes o solicitudes de patente EP2777178B1, WO2022/039758, US7463181B2, US8483578B2, US6297764B1 y US10039498B2 se conocen otros sistemas/dispositivos de filtrado, ópticos, para eliminación de diferentes tipos de interferencias. A pesar de que existen filtros adaptados para múltiples sectores, todavía se requieren nuevos sistemas/métodos para detección de interferencias en comunicaciones ópticas. Exposición de la invención A tal fin, ejemplos de realización de la presente invención aportan, de acuerdo a un primer aspecto, un sistema para detección de interferencias en comunicaciones ópticas. El sistema incluye un filtro adaptado configurado para eliminar interferencias causadas por una o más fuentes de luz en una señal digital recibida mediante la realización de una operación de filtrado sobre dicha señal digital recibida. La señal digital recibida comprende un patrón de pulsos, aleatorio y desconocido, emitido a través de un canal óptico, y la operación de filtrado comprende aplicar un filtrado paso bajo adaptado al atrón de pulsos y correlacionar e invertir en el tiempo el patrón de pulsos con la señal digital recibida. Ejemplos de realización de la presente invención también proporcionan, según un segundo aspecto, un método para detección de interferencias en comunicaciones ópticas. El método comprende eliminar, utilizando un filtro adaptado, interferencias causadas por una o más fuentes de luz en una señal digital recibida, mediante la realización de una operación de filtrado sobre dicha señal digital recibida, en donde la señal digital recibida comprende un patrón de pulsos, aleatorio y desconocido, emitido a través de un canal óptico, y en donde la operación de filtrado comprende aplicar un filtrado paso bajo adaptado a dicho patrón de pulsos y correlacionar e invertir en el tiempo el patrón de pulsos con la señal digital recibida. Según la presente invención, el filtro adaptado está incluido en un receptor, y particularmente está implementado mediante un procesador de señal digital (DSP) . En un ejemplo de realización, la operación de filtrado comprende, además: acumular, mediante un módulo acumulador, la señal digital recibida para un determinado orden; normalizar dicha acumulación mediante un módulo divisor; y acondicionar unos valores de salida del módulo divisor mediante un módulo de mapeo. En un ejemplo de realización, el sistema incluye también un conversor analógico digital configurado para recibir una señal analógica y convertirla en dicha señal digital. En algunos ejemplos, la señal analógica, previamente a la conversión, es escalada y adaptada a unos determinados valores de potencia. En un ejemplo de realización, el sistema incluye también un muestreador, dispuesto a la salida del filtro adaptado, y configurado para sincronizar unas señales de captura de muestreo de una señal de salida del filtro adaptado, tanto para una frecuencia como una fase de la señal de salida. En un ejemplo de realización, el muestreador está configurado para realizar la sincronización de la fase de la señal de salida mediante la implementación de un algoritmo que calcula un error de fase entre las señales de captura de muestreo y una señal de captura de muestreo óptima, y realiza un desplazamiento de la fase de muestreo hasta que las señales de captura de muestreo se realicen en un instante de muestreo de máxima relación señal a ruido. Particularmente, el muestreador también está implementado mediante un DSP. Otras realizaciones de la invención que se describen en el presente documento incluyen también productos de programas de ordenador o informáticos para realizar las etapas y operaciones del método propuesto en el segundo aspecto de la invención. Más particularmente, un producto de programa de ordenador es una realización que tiene un medio legible por ordenador que incluye instrucciones de programa informático codificadas en el mismo que cuando se ejecutan en al menos un procesador de un sistema informático producen al procesador realizar las operaciones indicadas en el presente documento como realizaciones de la invención. Por lo tanto, la presente invención es capaz de detectar un patrón conocido en una señal aleatoria y desconocida, maximizando la relación señal a ruido en un instante de muestreo determinado y cuya muestra será la que posteriormente habrá a la entrada de un decisor. Por ello, es muy útil para detectar los patrones, que en este caso serán los pulsos generados por el transmisor y emitidos al canal. Asimismo, la presente invención permite maximizar la SNR en presencia de ruido blanco aditivo y gaussiano, en comunicaciones ópticas, LIFI (Light Fidelity) en entornos exteriores y en movimiento. Lo que permite mejorar la señal de datos, aumentando la distancia de comunicación en comparación con los esquemas convencionales. El filtro adaptado propuesto es de particular relevancia en comunicaciones entre dos vehículos (V2V) o entre vehículos e infraestructuras (V2I) , eliminando por completo las interferencias introducidas por otras fuentes luminosas, incluida la peor de las interferencias, la solar. Igualmente, el filtro adaptado puede utilizarse en comunicaciones subacuáticas, de interior, o incluso la implantación de comunicaciones LIFI en vehículos aéreos, los cuales están enormemente limitados por las interferencias de radiofrecuencia. Breve descripción de los dibujos Las anteriores y otras características y ventajas se comprenderán más plenamente a partir de la siguiente descripción detallada de unos ejemplos de realización, meramente ilustrativa y no limitativa, con referencia a los dibujos que la acompañan, en los que: La Fig. 1 es un diagrama de bloques de un sistema para detección de interferencias en comunicaciones ópticas, según un ejemplo de realización de la presente invención. La Fig. 2 ilustra un ejemplo de una señal que puede ser transmitida al sistema propuesto. La Fig. 3 ilustra el comportamiento de cada bloque del sistema para una SNR en recepción de 25dB. La Fig. 4 ilustra el comportamiento de cada bloque del sistema para una SNR en recepción de 0dB. La Fig. 5 ilustra el comportamiento de cada bloque del sistema para una SNR en recepción de -10dB. La Fig. 6 ilustra diferentes casos de muestreo utilizando el algoritmo Early-late, según un ejemplo de realización de la presente invención. La Fig. 7 ilustra diferentes casos de muestreo utilizando el algoritmo Gardner, según un ejemplo de realización de la presente invención. La Fig. 8 ilustra otro ejemplo de realización del sistema propuesto. La Fig. 9 ilustra, esquemáticamente, el filtro adaptado, según un ejemplo de realización de la presente invención. La Fig. 10 ilustra, esquemáticamente, el módulo acumulador, según un ejemplo de realización de la presente invención. La Fig. 11 es un esquemático del corte (slice) DSP equivalente al módulo divisor, según un ejemplo de realización de la presente invención. La Fig. 12 ilustra, esquemáticamente, el módulo de mapeo, según un ejemplo de realización de la presente invención. La Fig. 13 ilustra, esquemáticamente, el muestreador, según un ejemplo de realización de la presente invención. La Fig. 14 ilustra, esquemáticamente, el módulo limitador, según un ejemplo de realización de la presente invención. La Fig. 15 ilustra, esquemáticamente, el módulo contador, según un ejemplo de realización de la presente invención. La Fig. 16 ilustra, esquemáticamente, el módulo comparador 1, o CMP1, mientras que la Fig. 17 ilustra el módulo comparador 2, o CMP2, según unos ejemplos de realización de la presente invención. La Fig. 18 ilustra, esquemáticamente, el módulo error, según un ejemplo de realización de la presente invención. La Fig. 19 es un esquemático del corte DSP del módulo error, según un ejemplo de realización de la presente invención. Descripción detallada de la invención y de unos ejemplos de realización La presente invención proporciona un sistema y un método para detección de interferencias (causadas por cualquier fuente de luz, o incluso interferencia debidas a la luz solar) en comunicaciones ópticas. En particular, la presente invención es muy eficaz para maximizar la SNR ante la presencia de ruido blanco, es decir, ruido cuyas muestras no mantienen correlación estadística en el dominio del tiempo, y por tanto su densidad espectral de potencia es constante. Para ello, la presente invención incluye/implementa un filtro adaptado (o matched filter) , lineal. El filtro adaptado (120) , particularmente implementado mediante software, por ejemplo, mediante un procesador de señal digital (DSP) , tal y como se explicará más adelante, mediante la realización de una operación de filtrado es capaz de detectar un patrón conocido en la señal aleatoria y desconocida recibida. Para ello, particularmente se correla el patrón que se quiere detectar invertido en el tiempo con la señal desconocida, o lo que es lo mismo, se convoluciona la señal desconocida con el patrón conocido conjugado e invertido en el tiempo. De esta forma, si se define la forma de pulso en transmisión como: Entonces, la respuesta ideal del filtro adaptado (120) es: Suponiendo una señal recibida x (t) , y teniendo en cuenta que aplicar el filtro adaptado (120) a dicha señal es equivalente a realizar una convolución entre la señal y el filtro, se puede calcular la expresión de la salida del filtro adaptado (120) como: Donde y (t) representa la salida del filtro adaptado (120) en el instante T. Teniendo en cuenta que hm (t) = h (T - t) , por tanto, si se sustituye en la ecuación 1.3, se obtiene la siguiente equivalencia: La expresión 1.4 se ha derivado de las expresiones 1.2 y 1.3, y equivale a la correlación cruzada de la señal recibida x (t) y el pulso en transmisión en el instante T. Este comportamiento del filtro adaptado (120) proporciona dos grandes ventajas. Por un lado, las formas de pulso generalmente están compuestas por bajas frecuencias, por tanto, la aplicación de un filtrado paso bajo a la señal en recepción permite el paso a estas formas de pulso que contienen la información relevante y atenúa las altas frecuencias que únicamente contienen ruido. La otra ventaja es la correlación que realiza el filtro de la señal en recepción con la forma de pulso en transmisión, detectando así cuando la señal recibida coincide con el patrón conocido. Con referencia ahora a la Fig. 1, en la misma se muestra un diagrama de bloques del sistema propuesto, según un ejemplo de realización. En este ejemplo, se ilustra un conversor analógico-digital de entrada (110) , el filtro adaptado (120) a la forma de pulso hm[n], y un bloque muestreador (130) , que se encarga de conseguir la recuperación de la sincronización. En las Figs. 3-5 se muestran varios ejemplos de la SNR en recepción utilizando el sistema anterior. En la Fig. 3, se ha simulado una SNR en recepción de 25dB. En la figura se puede ver una ligera oscilación en la señal recibida x (t) (10) (ver Fig.2 para un ejemplo de la misma) , debido al ruido añadido. En la señal de salida del filtro adaptado (120) f[n] (21) se genera el resultado de la acumulación durante el período completo. Finalmente, el muestreador (130) captura las muestras en los instantes óptimos, nT, de máxima SNR. La recuperación de los datos es correcta. En la Fig. 4, se muestra la misma simulación para una SNR en recepción de 0dB. Si se observa la señal recibida aparece muy distorsionada, sin embargo, el filtro adaptado (120) recupera correctamente los datos originales, en los instantes de máxima SNR. La recuperación sigue siendo correcta. En la Fig. 5, se muestra la misma simulación para una SNR en recepción de -10dB. La señal recibida ya es totalmente irreconocible de forma visual, el filtro adaptado (120) ecupera correctamente los datos originales, pero con mayor dificultad. Por ejemplo, la muestra capturada en el instante t = 3T, podría tener un valor aproximado de 0.5V, lo que se interpretaría correctamente por el decisor como un nivel alto, pero la diferencia es mucho menor que en la simulación con una SNR de 25dB. La recuperación sigue siendo correcta. En algunos ejemplos de realización, se realiza, preferiblemente en la parte analógica, una etapa de control automático de ganancia. Esta etapa se encarga de escalar, de forma automática y adaptada, la señal recibida (10) a unos valores de potencia conocidos. De esta manera, si la señal recibida (10) tiene una potencia demasiado alta se evita la introducción de distorsión (clipping) por el conversor analógico-digital (110) ; por el contrario, si la señal recibida (10) tiene una potencia demasiado baja se evita una pérdida de precisión a la hora de recuperar la información relevante. El bloque muestreador (130) , es el encargado de la recuperación de sincronización tanto en frecuencia, como en fase. La frecuencia en transmisión es conocida por el receptor, la sincronización en fase, en cambio, es desconocida y debe tenerse en cuenta. En un ejemplo de realización, para conseguir la sincronización en fase se desplaza la fase de muestreo sobre la salida (21) del filtro adaptado (120) hasta que las capturas se realicen en los instantes de máxima relación señal a ruido o SNR. Para ello, por un lado, se mide el error en fase que se está cometiendo entre la captura realizada y la captura óptima, es decir, se realiza la corrección de fase sobre la señal de muestreo. Por otro lado, se desplaza la fase de muestreo. De estas dos tareas se encarga el bloque muestreador (130) . En un ejemplo de realización, para medir el error en fase que se está cometiendo en el muestreo se utiliza un algoritmo de recuperación de sincronización, tal y como el algoritmo Early-late gate o el algoritmo Gardner. El algoritmo Early-late calcula el error a partir de muestras que están adelantadas y atrasadas respecto al punto de muestreo ideal. Para implementar este algoritmo es necesario tomar 3 muestras en cada período de símbolo, la muestra adelantada, la atrasada y la salida (31) del filtro adaptado (120) que es la que cae en medio. Para calcular el error se puede utilizar la siguiente ecuación: La salida de este algoritmo es la muestra yn_1. En la Fig. 6, aparecen 6 casos de muestreo con el algoritmo Early-late. Los 3 casos superiores ( (a) muestreo adelantado, (b) atrasado y (c) óptimo, respectivamente) son casos en los que el cálculo del error se realiza sobre un pico positivo, los 3 inferiores ( (d) muestreo adelantado, (e) atrasado y (f) óptimo, respectivamente) sobre un pico negativo. Para estos ejemplos se ha supuesto una señal bipolar de ±1V. Si se calcula el error que devuelve la ecuación del algoritmo Early-late para cada uno de los ejemplos en las figuras, se obtienen los siguientes resultados: De esta forma, se puede concluir que haciendo uso del algoritmo Early-Late, la corrección que se debe realizar a la fase de muestreo es el valor devuelto por la ecuación 1.5, aplicando la correspondiente normalización en amplitud. El algoritmo de Gardner está muy extendido y es frecuente su uso en sistemas de recuperación de sincronismo. Gardner utiliza 2 muestras por período de símbolo y para calcular el error utiliza la ecuación 1.5, al igual que el algoritmo Early-late. La salida de este algoritmo es la muestra yn . La separación temporal entre las muestras exteriores, y 2 es de un período de bit, y la separación temporal entre las muestras consecutivas, es de medio período de bit. Es importante destacar que la ecuación de Gardner necesita muestrear sobre una señal bipolar para que el error calculado sea correcto. En la Fig. 7 se pueden observar 6 casos de muestreo con el algoritmo de Gardner. Los 3 casos superiores ( (a) muestreo adelantado, (b) atrasado y (c) óptimo, respectivamente) son casos en los que el cálculo del error se realizará sobre una pendiente negativa, los 3 inferiores ( (d) muestreo adelantado, (e) atrasado y (f) óptimo, respectivamente) son casos con pendiente positiva. Para estos ejemplos se ha supuesto una señal bipolar de ±1 V. Si se calcula el error que devuelve la ecuación de Gardner para cada uno de los ejemplos en las figuras, se obtienen los siguientes resultados: El resultado de las ecuaciones aporta dos datos importantes, uno es la amplitud del error que se está cometiendo en el muestreo y el otro es el signo del error, que revelará la dirección en la que se deberá corregir la fase de muestreo. En el caso de Gardner, el signo que devuelve la ecuación del error es contrario al signo del incremento a realizar sobre la fase de muestreo. De esta forma, se puede concluir que haciendo uso del algoritmo Gardner, la corrección que se debe realizar a la fase de muestreo es la negación del valor devuelto por la ecuación 1.5, aplicando la correspondiente normalización en amplitud. Con referencia ahora a la Fig. 8, en la misma se muestra otro ejemplo de realización del sistema propuesto. Según este ejemplo de realización, los datos de entrada (capturados por el citado conversor analógico-digital 110) entran al filtro adaptado (120) para que éste genere una señal de acumulación. El bloque muestreador (130) se encarga de generar durante un período de reloj, tres señales de habilitación de reloj (o clock enable) diferentes, que habilitarán, independientemente, cada uno de los 3 registros que aparecen en paralelo para realizar las diferentes capturas de la salida del filtro adaptado (120) . Como se puede observar, del bloque muestreador (130) salen 3 señales de habilitación de reloj, cada una para capturar las 3 muestras necesarias durante el período de bit y posteriormente calcular el error. El bloque de error 140 aplica la ecuación 1.5, y su salida es capturada por un registro cuando se activa CE2, este registro es útil para evitar los fallos (glitches) que se producen mientras se capturan los datos y se calcula el resultado de la operación. Una vez el error es capturado por el registro, el bloque muestreador (130) realiza un desfase de las tres señales de habilitación de reloj para, iteración tras iteración, converger a una fase óptima de sincronización. Finalmente, la señal MODE sirve para implementar el algoritmo de recuperación de sincronización. El muestreador (130) , alterna entre sumar o restar el error calculado y registrado. El multiplexor alterna la salida del filtro adaptado, pudiendo seleccionar entre la muestra S2 o la muestra S3. En este ejemplo de realización, el filtro adaptado (120) se encarga de acumular la señal de entrada de forma discreta para un orden definido, normalizar esta acumulación y finalmente realizar un mapeo de los datos de salida para acondicionarlos a los bloques posteriores. Estas operaciones están divididas en tres diferentes módulos/bloques, tal y como se muestra en la Fig. 9, particularmente implementados con cortes DSP. El módulo o bloque acumulador (121) se encarga de implementar la ecuación 1.6, que es la expresión equivalente a un acumulador de orden N, donde x[n] es la entrada, acc[n] es la acumulación realimentada y y[n] la salida: La implementación de dicha expresión matemática da como resultado el esquemático que se muestra en la Fig. 10. Para implementar este esquemático, se debe hacer uso de un registro de desplazamiento capaz de almacenar las muestras retrasadas en el tiempo, además de un corte DSP que se encargará de realizar la suma y resta necesaria. El módulo o bloque divisor (122) permite normalizar la acumulación. Su funcionamiento se basa en un corte DSP, por lo que se representará el esquemático de la configuración del DSP directamente. Dicho esquemático se puede ver en la Fig. 11. Asimismo, se realiza una multiplicación decimal en punto flotante para poder normalizar. Suponiendo la expresión (1.7) como la salida del módulo acumulador (121) en la que acc representa la acumulación, N el orden del filtro y x el dato de entrada, el valor que se desea obtener tras el módulo divisor (122) será el representado por la expresión (1.8) , donde div equivale a la salida del módulo divisor (122) : Para ello, se multiplica la salida del acumulador por un valor constante definido como el inverso del orden del filtro, particularmente desplazado 17 bits a la izquierda. En un ejemplo de realización, según la Fig. 11, la operación equivalente que realiza el corte DSP es: El módulo o bloque de mapeo (123) se encarga de acondicionar los valores de salida del divisor (122) para que sean interpretables de forma correcta por los bloques posteriores. Esta etapa es necesaria debido a que el conversor analógico-digital (110) ofrece valores entre [0, 16383], y la señal de acumulación debe ser bipolar. Por tanto, el mapeo particularmente se realiza desde un dominio [0, 16383] hacia un dominio [8192.- 8191], obteniendo así un escalado bipolar y aprovechando toda la resolución del conversor (110) . La operación matemática que debe realizar este módulo de mapeo (123) aparece reflejada en la ecuación 1.10, donde map representa la salida del módulo de mapeo (123) y div la salida del divisor (122) . La configuración del módulo de mapeo (123) y, por tanto, del DSP asociado a este, se puede ver en la Fig. 12. Se puede observar como la entrada del multiplexor Z es PCIN, es decir, el bus dedicado para interconectar los cortes DSP de forma directa sin rutado adicional, además, está seleccionada con un desplazamiento de 17 bits hacia la derecha, este desplazamiento es necesario para rectificar la operación realizada previamente por el módulo divisor (122) . Con referencia ahora a la Fig. 13, en la misma se ilustra un ejemplo de realización particular del muestreador (130) . El muestreador (130) toma un valor de cuenta límite, e implementa un contador que se incrementa hasta alcanzar dicho valor límite y una vez alcanzado, se reinicia a cero, siendo éste, el período del ciclo de cuenta. Durante cada ciclo de cuenta, se encarga de generar 3 señales activas durante un período de reloj, denominadas CE1, CE2 y CE3, que capturan cada una de las muestras necesarias para calcular el error. Más específicamente, el módulo limitador (131) se encarga de calcular el valor límite de cuenta para cada ciclo, el módulo contador (132) implementa un contador unitario que se resetea cuando alcanza el valor límite proporcionado por el módulo limitador (131) . A través de las señales COUNT1 y COUNT2 se transmite el valor de cuenta a los bloques CMP1 (133) y CMP2 (134) . Estos dos módulos son internamente idénticos y son comparadores que activan su salida cuando sus dos valores de entrada coinciden. La Fig. 14 muestra un ejemplo de realización particular del módulo limitador (131) . Este bloque se encarga de modificar el valor de cuenta límite para cada ciclo, pudiendo así contar un valor mayor o menor al período de bit. El límite de cuenta equivalente al período de bit se le proporciona por la entrada COUNT_LIMIT, de esta forma se consigue esplazar la fase de muestreo hacia delante o hacia atrás. La corrección de fase realizada será el error calculado por el módulo ERROR 140. La entrada MODE sirve para sumar o restar el error de entrada sobre el valor de COUNT_LIMIT, por tanto, permite alternar entre el algoritmo Early-Late y Gardner (es decir, entre un algoritmo de sincronización u otro) . La Fig. 15 muestra un ejemplo de realización particular del módulo contador (132) . Este elemento se encarga de incrementar de forma unitaria un valor de cuenta y ofrecer dicho valor de cuenta a su salida. Además, incluye un detector de patrones configurado para que la cuenta se reinicie a cero cuando alcance el valor COUNT_LIMIT. La propia señal PATTERN DETECT que ofrece el corte DSP es útil para detectar cuando la cuenta ha llegado al límite, precisamente en ese instante es cuando interesa capturar la tercera muestra, por lo tanto, la salida PATTERN DETECT será CE3. Los bloques comparadores CMP1 (133) y CMP2 (134) están implementados también sobre cortes DSP. El módulo CMP1 (133) transmite el valor de cuenta a través del bus PCIN interno, al módulo CMP2 (134) , de forma que ambos conocen el valor de cuenta. Internamente, cada comparador compara el valor de cuenta con el valor de threshold o límite que tiene a su entrada, de esta forma, si se diseñan los valores de threshold, tal y como se muestra en la Fig. 13, se consigue que el comparador CMP1 (133) se active justo al inicio de cada ciclo y el comparador CMP2 (134) se active justo en la mitad. Estas señales serán CE1 y CE2 respectivamente. En la Figs. 16 y 17 se pueden ver las configuraciones de los cortes DSP correspondientes a los bloques CMP1 y CMP2 respectivamente. Con referencia ahora a las Figs. 18 y 19, en las mismas se ilustra unos ejemplos del bloque error (140) . Este módulo (140) está formado por un único corte DSP y se encarga de calcular el error a partir de las tres muestras capturadas sobre la señal de acumulación del pulso. Para ello, implementa la ecuación (1.5) y ofrece a su salida el resultado de dicha ecuación dividido por un valor potencia de 2 configurable. Preferiblemente, este factor es potencia de 2 para que la división se pueda implementar de forma sencilla como desplazamiento de bits. En dichas figuras, se presentan tres muestras como entrada y el error calculado como salida. Las operaciones que realiza el bloque error (140) son la ecuación del error en el corte DSP y posteriormente el desplazamiento para dividir. Para generalizar el valor de division DIV, se utiliza la siguiente ecuación: La invención propuesta puede implementarse en hardware, software, firmware o cualquier combinación de los mismos. Si se implementa en software, las funciones pueden almacenarse en o codificarse como una o más instrucciones o código en un medio legible por ordenador. Como se usa en el presente documento, los productos de programa de ordenador que comprenden medios legibles por ordenador incluyen todas las formas de medio legible por ordenador excepto, hasta el punto de que ese medio se considere que no son señales de propagación transitorias no establecidas. El alcance de la presente invención está definido en las reivindicaciones adjuntas.

Publicaciones:

ES2953591 (14/11/2023) - A1 Solicitud de patente con informe sobre el estado de la técnica

Eventos:

En fecha 30/03/2022 se realizó Registro Instancia de Solicitud

En fecha 31/03/2022 se realizó Admisión a Trámite

En fecha 31/03/2022 se realizó 1001P_Comunicación Admisión a Trámite

En fecha 21/04/2022 se realizó Defectos en solicitud de reducción de tasas

En fecha 21/04/2022 se realizó 6100X_Notificación defectos en solicitud de reducción de tasas

En fecha 27/04/2022 se realizó Publicación defectos en solicitud de reducción de tasas

En fecha 23/06/2022 se realizó 3007_Registro subsanación de defectos en reducción de tasas

En fecha 01/07/2022 se realizó Concesión solicitud de reducción de tasas

En fecha 05/07/2022 se realizó Superado examen de oficio

En fecha 07/07/2022 se realizó Publicación concesión reducción de tasas

En fecha 30/11/2022 se realizó Realizado IET

En fecha 02/12/2022 se realizó 1109P_Comunicación Traslado del IET

En fecha 14/11/2023 se realizó Publicación Solicitud

En fecha 14/11/2023 se realizó Publicación Folleto Solicitud con IET (A1)

En fecha 12/02/2024 se realizó Registro Documentación no Identificada

En fecha 12/02/2024 se realizó 5215P_Observaciones del solicitante al IET, Opinión Escrita y/o alegaciones a observaciones de terceros

En fecha 13/02/2024 se realizó PETEX_Petición de examen sustantivo

En fecha 29/02/2024 se realizó Validación petición y/o pago de examen sustantivo conforme

En fecha 29/02/2024 se realizó El solicitante ha contestado pero existen nuevas objeciones a la concesión de la solicitud

En fecha 29/02/2024 se realizó Elaboración de examen sustantivo

En fecha 29/02/2024 se realizó 6120P_Notificación de examen sustantivo

En fecha 06/03/2024 se realizó Publicación de examen sustantivo

Pagos:

30/03/2022 - Pago Tasas IET

Fuente de la información

Parte de la información aquí publicada es pública puesto que ha sido obtenida de la Oficina de Propiedad Industrial de los diferentes países el 29/04/2024 y por lo tanto puede ser que la información no esté actualizada.Parte de la información aquí mostrada ha sido calculada por nuestro sistema informático y puede no ser veraz.

Privacidad

Si considera que al información aquí publicada afecta a su privacidad y desea que eliminemos la información aquí publicada envíe un email a info@patentes-y-marcas.com o rellene el formulario que encontrará aquí.Información sobre el registro de patente nacional por SISTEMA, MÉTODO Y PROGRAMA DE ORDENADOR PARA DETECCIÓN DE INTERFERENCIAS EN COMUNICACIONES ÓPTICAS con el número P202230289

El registro de patente nacional por SISTEMA, MÉTODO Y PROGRAMA DE ORDENADOR PARA DETECCIÓN DE INTERFERENCIAS EN COMUNICACIONES ÓPTICAS con el número P202230289 fue solicitada el 30/03/2022. Se trata de un registro en España por lo que este registro no ofrece protección en el resto de países. El registro SISTEMA, MÉTODO Y PROGRAMA DE ORDENADOR PARA DETECCIÓN DE INTERFERENCIAS EN COMUNICACIONES ÓPTICAS con el número P202230289 fue solicitada por DATLIGHT, S.L. mediante los servicios del agente Eli SALIS. El registro [modality] por SISTEMA, MÉTODO Y PROGRAMA DE ORDENADOR PARA DETECCIÓN DE INTERFERENCIAS EN COMUNICACIONES ÓPTICAS con el número P202230289 está clasificado como H04B 10/07 según la clasificación internacional de patentes.

Otras invenciones solicitadas por DATLIGHT, S.L.

Es posible conocer todas las invenciones solicitadas por DATLIGHT, S.L. entre las que se encuentra el registro de patente nacional por SISTEMA, MÉTODO Y PROGRAMA DE ORDENADOR PARA DETECCIÓN DE INTERFERENCIAS EN COMUNICACIONES ÓPTICAS con el número P202230289. Si se desean conocer más invenciones solicitadas por DATLIGHT, S.L. clicar aquí.Otras invenciones solicitadas en la clasificación internacional de patentes H04B 10/07.

Es posible conocer invenciones similares al campo de la técnica se refiere. El registro de patente nacional por SISTEMA, MÉTODO Y PROGRAMA DE ORDENADOR PARA DETECCIÓN DE INTERFERENCIAS EN COMUNICACIONES ÓPTICAS con el número P202230289 está clasificado con la clasificación H04B 10/07 por lo que si se desea conocer más registros con la clasificación H04B 10/07 clicar aquí.Otras invenciones solicitadas a través del representante ELI SALIS

Es posible conocer todas las invenciones solicitadas a través del agente ELI SALIS entre las que se encuentra el registro patente nacional por SISTEMA, MÉTODO Y PROGRAMA DE ORDENADOR PARA DETECCIÓN DE INTERFERENCIAS EN COMUNICACIONES ÓPTICAS con el número P202230289. Si se desean conocer más invenciones solicitadas a través del agente ELI SALIS clicar aquí.Patentes en España

Es posible conocer todas las invenciones publicadas en España entre las que se encuentra el registro patente nacional por SISTEMA, MÉTODO Y PROGRAMA DE ORDENADOR PARA DETECCIÓN DE INTERFERENCIAS EN COMUNICACIONES ÓPTICAS. Nuestro portal www.patentes-y-marcas.com ofrece acceso a las publicaciones de patentes en España. Conocer las patentes registradas en un país es importante para saber las posibilidades de fabricar, vender o explotar una invención en España.Patentes registradas en la clase H

Es posible conocer todas las patentes registradas en la clase H (ELECTRICIDAD) entre las que se encuentra la patente SISTEMA, MÉTODO Y PROGRAMA DE ORDENADOR PARA DETECCIÓN DE INTERFERENCIAS EN COMUNICACIONES ÓPTICAS con el número P202230289. Conocer las patentes registradas en una clase es importante para saber las posibilidades de registrar una patente en esa misma clase.Patentes registradas en la clase H04

Es posible conocer todas las patentes registradas en la clase H04 (TECNICA DE LAS COMUNICACIONES ELECTRICAS) entre las que se encuentra la patente SISTEMA, MÉTODO Y PROGRAMA DE ORDENADOR PARA DETECCIÓN DE INTERFERENCIAS EN COMUNICACIONES ÓPTICAS con el número P202230289. Conocer las patentes registradas en una clase es importante para saber las posibilidades de registrar una patente en esa misma clase.Patentes registradas en la clase H04B

Es posible conocer todas las patentes registradas en la clase H04B (TRANSMISION) entre las que se encuentra la patente SISTEMA, MÉTODO Y PROGRAMA DE ORDENADOR PARA DETECCIÓN DE INTERFERENCIAS EN COMUNICACIONES ÓPTICAS con el número P202230289. Conocer las patentes registradas en una clase es importante para saber las posibilidades de registrar una patente en esa misma clase.

¿Tienes alguna duda?

Escribe tu consulta y te responderemos rápida y gratuitamente.

P202230284

P202230284